- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄199495 > TSPC860SRMZPU40D4 (E2V TECHNOLOGIES PLC) 32-BIT, 40 MHz, RISC PROCESSOR, PBGA357 PDF資料下載

參數(shù)資料

| 型號(hào): | TSPC860SRMZPU40D4 |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 40 MHz, RISC PROCESSOR, PBGA357 |

| 封裝: | PLASTIC, BGA-357 |

| 文件頁數(shù): | 4/90頁 |

| 文件大小: | 2351K |

| 代理商: | TSPC860SRMZPU40D4 |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

12

TSPC860

2129A–HIREL–08/02

BG

Hi-Z

E2

Bidirectional

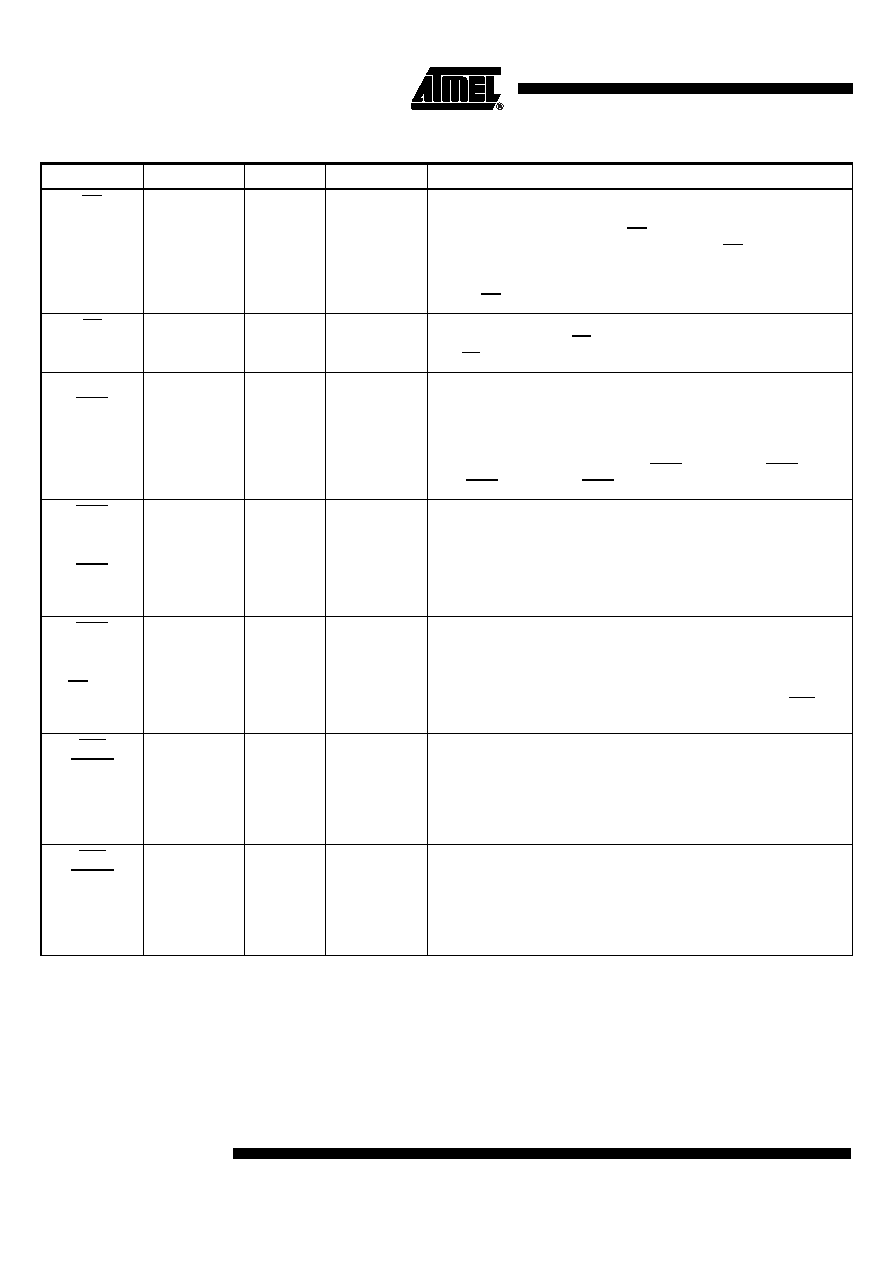

Bus Grant — Asserted low when the arbiter of the external bus

grants the bus to a specific device. When the TSPC860 is configured

to work with the internal arbiter, BG is configured as an output and

asserted every time the external master asserts BR and its priority

request is higher than any internal sources requiring a bus transfer.

However, when the TSPC860 is configured to work with an external

arbiter, BG is an input.

BB

Hi-Z

E1

Bidirectional

Active Pull-up

Bus Busy — Asserted low by a master to show that it owns the bus.

The TSPC860 asserts BB after the arbiter grants it bus ownership

and BB is negated.

FRZ

IRQ6

See Section

G3

Bidirectional

Freeze — Output asserted to indicate that the core is in debug

mode.

Interrupt Request 6 — One of eight external inputs that can request

(by means of the internal interrupt controller) a service routine from

the core. Note that the interrupt request signal sent to the interrupt

controller is the logical AND of FRZ/IRQ6 (if defined as IRQ6) and

DP3/IRQ6 (if defined as IRQ6).

IRQ0

Hi-Z

V14

Input

Interrupt Request 0 — One of eight external inputs that can request

(by means of the internal interrupt controller) a service routine from

the core.

IRQ1

Hi-Z

U14

Input

Interrupt Request 1 — One of eight external inputs that can request

(by means of the internal interrupt controller) a service routine from

the core.

IRQ7

Hi-Z

W15

Input

Interrupt Request 7 — One of eight external inputs that can request

(by means of the internal interrupt controller) a service routine from

the core.

CS(0-5)

High

C3, A2,

D4, E4,

A4, B4

Output

Chip Select — These outputs enable peripheral or memory devices

at programmed addresses if they are appropriately defined. CS0 can

be configured to be the global chip-select for the boot device.

CS6

CE1_B

High

D5

Output

Chip Select 6 — This output enables a peripheral or memory device

at a programmed address if defined appropriately in the BR6 and

OR6 in the memory controller.

Card Enable 1 Slot B — This output enables even byte transfers

when accesses to the PCMCIA Slot B are handled under the control

of the PCMCIA interface.

CS7

CE2_B

High

C4

Output

Chip Select 7 — This output enables a peripheral or memory device

at a programmed address if defined appropriately in the BR7 and

OR7 in the memory controller.

Card Enable 2 Slot B — This output enables odd byte transfers

when accesses to the PCMCIA Slot B are handled under the control

of the PCMCIA interface.

Table 1. Signal Descriptions (Continued)

Name

Reset

Number

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC860SRMZPU50D4 | 32-BIT, 50 MHz, RISC PROCESSOR, PBGA357 |

| TSPD11CGVRA0 | PUSHBUTTON SWITCH, SPST, MOMENTARY, 0.02A, 20VDC, THROUGH HOLE-RIGHT ANGLE |

| 2-1437573-9 | PUSHBUTTON SWITCH, SPDT, MOMENTARY, 0.02A, 20VDC, SURFACE MOUNT-RIGHT ANGLE |

| 3-1437573-4 | PUSHBUTTON SWITCH, SPST, MOMENTARY, 0.02A, 20VDC, THROUGH HOLE-RIGHT ANGLE |

| TSPF5400AS21 | 5 mm, 1 ELEMENT, INFRARED LED, 870 nm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC860SRMZQU66D | 制造商:e2v technologies 功能描述:MPU RISC 32BIT 66MHZ 3.3V 357BGA - Trays |

| TSPC860SRVZQU66D | 制造商:e2v technologies 功能描述:TSPC860SRVZQU66D - Trays |

| TSPC860XRMZPU66D | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Integrated Communication Processor |

| TSPC860XRMZQU66D | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Integrated Communication Processor |

| TSPC860XRVZPU66D | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Integrated Communication Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。