- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383963 > TPS3600x33PWR (Texas Instruments, Inc.) BATTERY-BACKUP SUPERVISORS FOR LOW-POWER PROCESSORS PDF資料下載

參數(shù)資料

| 型號: | TPS3600x33PWR |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | BATTERY-BACKUP SUPERVISORS FOR LOW-POWER PROCESSORS |

| 中文描述: | 電池備份監(jiān)事的低功耗處理器 |

| 文件頁數(shù): | 7/26頁 |

| 文件大小: | 510K |

| 代理商: | TPS3600X33PWR |

SLVS336B DECEMBER 2000 REVISED JANUARY 2007

7

detailed description (continued)

25

μ

s

200 ms

100

μ

A

t

IBAT

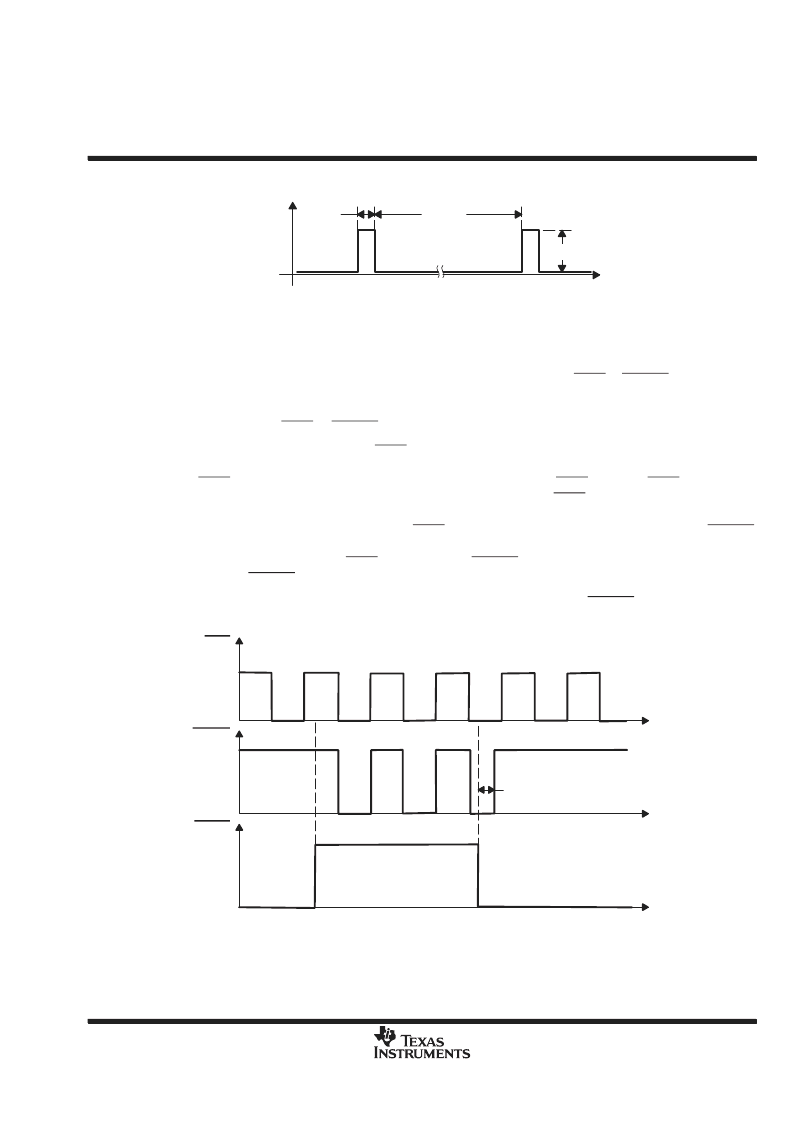

Figure 1. BATTOK Timing

chip-enable signal gating

The internal gating of chip-enable signals (CE) prevents erroneous data from corrupting CMOS RAM during

an under-voltage condition. The TPS3600 use a series transmission gate from CEIN to CEOUT. During normal

operation (reset not asserted), the CE transmission gate is enabled and passes all CE transitions. When reset

is asserted, this path becomes disabled, preventing erroneous data from corrupting the CMOS RAM. The short

CE propagation delay from CEIN to CEOUT enables the TPS3600 devices to be used with most processors.

The CE transmission gate is disabled and CEIN is high impedance (disable mode) while reset is asserted.

During a power-down sequence when V

DD

crosses the reset threshold, the CE transmission gate will be

disabled and CEIN immediately becomes high impedance if the voltage at CEIN is high. If CEIN is low during

reset is asserted, the CE transmission gate will be disabled same time when CEIN goes high, or 15

μ

s after reset

asserts, whichever occurs first. This will allow the current write cycle to complete during power down. When the

CE transmission gate is enabled, the impedance of CEIN appears as a resistor in series with the load at CEOUT.

The overall device propagation delay through the CE transmission gate depends on V

OUT

, the source

impedance of the device connected to CEIN and the load at CEOUT. To achieve minimum propagation delay,

the capacitive load at CEOUT should be minimized, and a low-output-impedance driver be used.

During disable mode, the transmission gate is off and an active pullup connects CEOUT to V

OUT

. This pullup

turns off when the transmission gate is enabled.

15

μ

s

CEIN

CEOUT

RESET

t

t

t

Figure 2. Chip-Enable Timing

www.ti.com

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS3600x50PW | BATTERY-BACKUP SUPERVISORS FOR LOW-POWER PROCESSORS |

| TPS3600x50PWR | BATTERY-BACKUP SUPERVISORS FOR LOW-POWER PROCESSORS |

| TPS3620-50DGK | BACKUP-BATTERY SUPERVISORS FOR RAM RETENTION |

| TPS3620-33DGK | BACKUP-BATTERY SUPERVISORS FOR RAM RETENTION |

| TPS3705-30Y | PROCESSOR SUPERVISORY CIRCUITS WITH POWER-FAIL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS3600X50PW | 制造商:TI 制造商全稱:Texas Instruments 功能描述:BATTERY-BACKUP SUPERVISORS FOR LOW-POWER PROCESSORS |

| TPS3600X50PWR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:BATTERY-BACKUP SUPERVISORS FOR LOW-POWER PROCESSORS |

| TPS3606-33 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:BATTERY-BACKUP SUPERVISOR FOR LOW-POWER PROCESSORS |

| TPS3606-33DGS | 功能描述:監(jiān)控電路 Battery-Backup for LP Processor RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| TPS3606-33DGSG4 | 功能描述:監(jiān)控電路 Battery-Backup for LP Processor RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。