- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382672 > TP3054 (National Semiconductor Corporation) “Enhanced” Serial Interface CMOS CODEC/Filter(加強(qiáng)型串行接口CMOS編解碼器/濾波器) PDF資料下載

參數(shù)資料

| 型號(hào): | TP3054 |

| 廠商: | National Semiconductor Corporation |

| 元件分類: | Codec |

| 英文描述: | “Enhanced” Serial Interface CMOS CODEC/Filter(加強(qiáng)型串行接口CMOS編解碼器/濾波器) |

| 中文描述: | “增強(qiáng)”串行接口的CMOS編解碼器/過濾器(加強(qiáng)型串行接口的CMOS編解碼器/濾波器) |

| 文件頁數(shù): | 6/16頁 |

| 文件大?。?/td> | 250K |

| 代理商: | TP3054 |

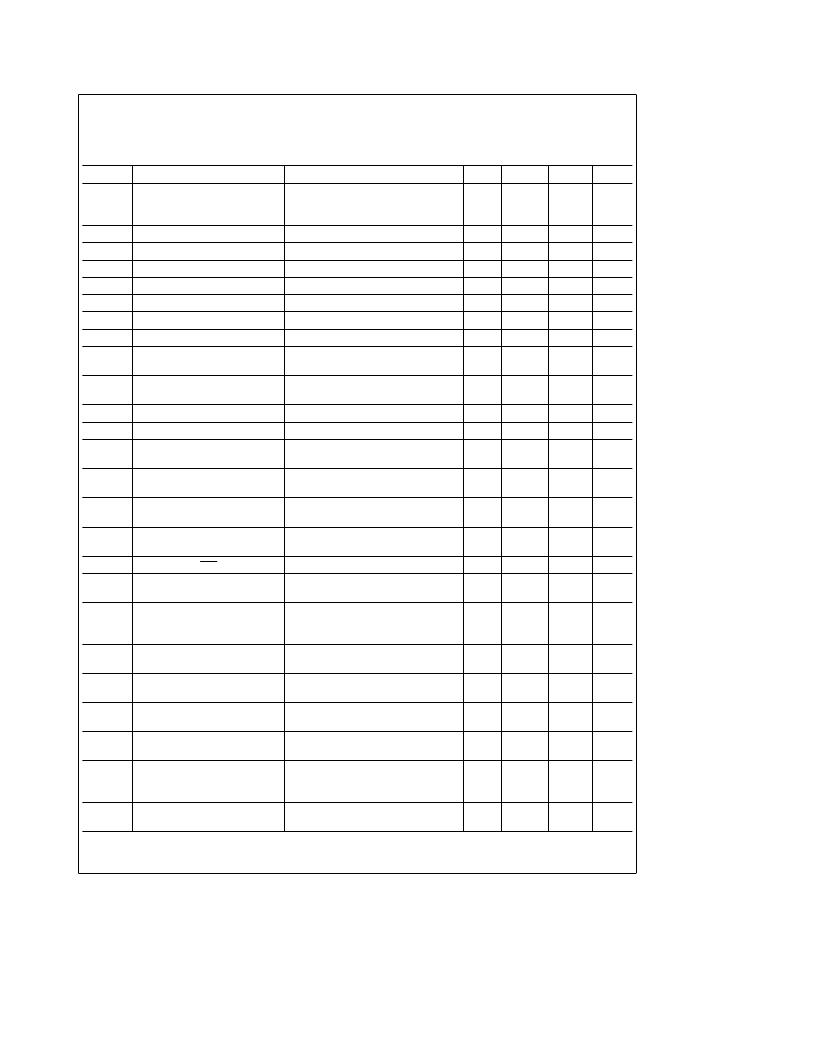

Timing Specifications

Unless otherwise noted, limits printed in

BOLD

characters are guaranteed for V

CC

e

5.0V

g

5%, V

BB

e b

5.0V

g

5%; T

A

e

0

§

C to 70

§

C by correlation with 100% electrical testing at T

A

e

25

§

C. All other limits are

assured by correlation with other production tests and/or product design and characterization. All signals referenced to GNDA.

Typicals specified at V

CC

e

5.0V, V

BB

e b

5.0V, T

A

e

25

§

C. All timing parameters are measured at V

OH

e

2.0V and V

OL

e

0.7V. See Definitions and Timing Conventions section for test methods information.

Symbol

Parameter

Conditions

Min

Typ

Max

Units

1/t

PM

Frequency of Master Clocks

Depends on the Device Used and the

BCLK

R

/CLKSEL Pin.

MCLK

X

and MCLK

R

1.536

1.544

2.048

MHz

MHz

MHz

t

RM

Rise Time of Master Clock

MCLK

X

and MCLK

R

50

ns

t

FM

Fall Time of Master Clock

MCLK

X

and MCLK

R

50

ns

t

PB

Period of Bit Clock

485

488

15725

ns

t

RB

Rise Time of Bit Clock

BCLK

X

and BCLK

R

50

ns

t

FB

Fall Time of Bit Clock

BCLK

X

and BCLK

R

50

ns

t

WMH

Width of Master Clock High

MCLK

X

and MCLK

R

160

ns

t

WML

Width of Master Clock Low

MCLK

X

and MCLK

R

160

ns

t

SBFM

Set-Up Time from BCLK

X

High

to MCLK

X

Falling Edge

First Bit Clock after the Leading

Edge of FS

X

100

ns

t

SFFM

Set-Up Time from FS

X

High

to MCLK

X

Falling Edge

Long Frame Only

100

ns

t

WBH

Width of Bit Clock High

V

IH

e

2.2V

160

ns

t

WBL

Width of Bit Clock Low

V

IL

e

0.6V

160

ns

t

HBFL

Holding Time from Bit Clock

Low to Frame Sync

Long Frame Only

0

ns

t

HBFS

Holding Time from Bit Clock

High to Frame Sync

Short Frame Only

0

ns

t

SFB

Set-Up Time from Frame Sync

to Bit Clock Low

Long Frame Only

80

ns

t

DBD

Delay Time from BCLK

X

High

to Data Valid

Load

e

150 pF plus 2 LSTTL Loads

0

140

ns

t

DBTS

Delay Time to TS

X

Low

Load

e

150 pF plus 2 LSTTL Loads

140

ns

t

DZC

Delay Time from BCLK

X

Low to

Data Output Disabled

C

L

e

0 pF to 150 pF

50

165

ns

t

DZF

Delay Time to Valid Data from

FS

X

or BCLK

X

, Whichever

Comes Later

C

L

e

0 pF to 150 pF

20

165

ns

t

SDB

Set-Up Time from D

R

Valid to

BCLK

R/X

Low

50

ns

t

HBD

Hold Time from BCLK

R/X

Low to

D

R

Invalid

50

ns

t

SF

Set-Up Time from FS

X/R

to

BCLK

X/R

Low

Short Frame Sync Pulse (1 Bit Clock

Period Long)

50

ns

t

HF

Hold Time from BCLK

X/R

Low

to FS

X/R

Low

Short Frame Sync Pulse (1 Bit Clock

Period Long)

100

ns

t

HBFl

Hold Time from 3rd Period of

Bit Clock Low to Frame Sync

(FS

X

or FS

R

)

Long Frame Sync Pulse (from 3 to 8 Bit

Clock Periods Long)

100

ns

t

WFL

Minimum Width of the Frame

Sync Pulse (Low Level)

64k Bit/s Operating Mode

160

ns

6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TP3056BDWR | PCM CODEC|SINGLE|CMOS|SOP|16PIN|PLASTIC |

| TP3056B | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3056BDW | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3056BN | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3098 | TRANSISTOR | BJT | NPN | 200MA I(C) | RFMOD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TP3054A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3054ADW | 功能描述:接口—CODEC PCM CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TP3054ADWR | 功能描述:接口—CODEC Mono Serial Intfc PCM Codec/Filter RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TP3054AJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:u-Law CODEC |

| TP3054AN | 功能描述:接口—CODEC PCM CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。