- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384012 > TMC22191KHC (FAIRCHILD SEMICONDUCTOR CORP) Digital Video Encoders/Layering Engine PDF資料下載

參數(shù)資料

| 型號(hào): | TMC22191KHC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | Digital Video Encoders/Layering Engine |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP100 |

| 封裝: | 3.20 MM HEIGHT, MQFP-100 |

| 文件頁數(shù): | 25/60頁 |

| 文件大?。?/td> | 293K |

| 代理商: | TMC22191KHC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

PRODUCT SPECIFICATION

TMC22091/TMC22191

25

Gamma Correction

Gamma is built into broadcast television systems as a correc-

tion factor for nonlinearity in image acquisition (nonlinear

conversion of light into current in a vidicon) and at the dis-

play (phosphor nonlinearity in converting current into light).

A Gamma corrector transfer function takes the form of

Output = k ( Input )

1/

γ

where a typical Gamma is 2.2 for NTSC, 2.8 for PAL.

Computer systems usually ignore Gamma in driving a dis-

play monitor. Each R, G, and B channel is treated as linear.

When encoding a computer display output to video, the user

must decide whether to apply a gamma correction factor and,

if so, what value. It is a good assumption that, since the digi-

tal video input over the CVBS bus is in composite form, it

has been Gamma corrected.

Gamma correction is applied in the RGB domain. When

operating in YC

B

C

R

, for example when encoding a CCIR-

601 signal, Gamma should have already been applied.

Gamma correction is readily added to the RGB transfer

equations shown in Table 4.

Video Timing

The TMC22x91 can be programmed to accommodate a wide

range of system timing requirements. With a line locked

pixel rate of 10 to 15 Mpps, the digitally synthesized hori-

zontal waveforms and subcarrier frequency and phase are

determined from 24 registers that are loaded by a controller.

Horizontal Programming

Horizontal interval timing is fully programmable, and is

established by loading the timing registers with the durations

of each horizontal element. The duration is expressed in

PCK clock cycles. In this way, any pixel clock rate between

10 MHz and 15 MHz can be accommodated, and any desired

standard or non-standard horizontal video timing may be

produced. Figure 3 illustrates the horizontal blanking inter-

val with timing register identification.

Horizontal timing parameters can be calculated as follows:

t = N x (PCK period)

= N x (2 x PXCK period)

where N is the value loaded into the appropriate timing reg-

ister, and PCK is the pixel clock period.

Horizontal timing resolution is two PXCK periods. PXCK

must be chosen such that it is an even integer multiple of the

horizontal line frequency. This ensures that the horizontal

line period, H, contains an integer number of pixels. The hor-

izontal line comprises the sum of appropriate elements.

H = FP + SY + BR + BU + CBP + VA

When programming horizontal timing, subtract 5 PCK

periods from the calculated values of CBP and add 5 PCK

periods to the calculated value for VA.

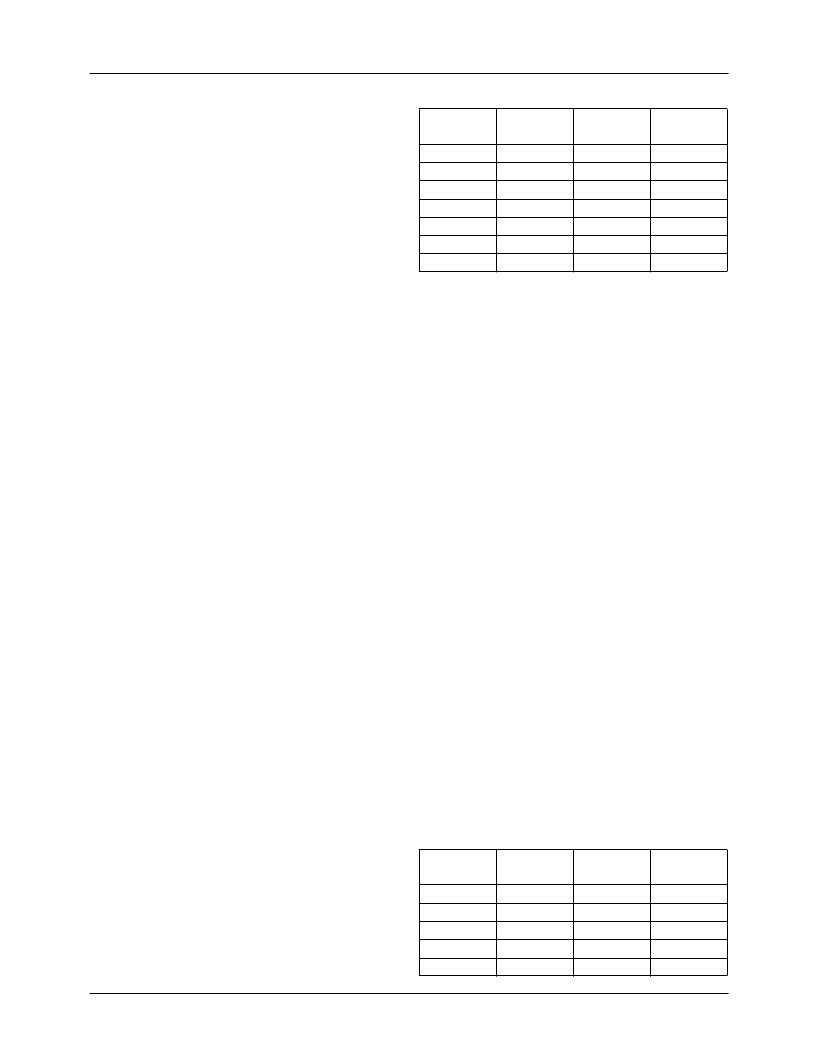

Table 7. Horizontal Timing Specifications

Vertical Programming

Vertical interval timing is also fully programmable, and is

established by loading the timing registers with the durations

of each vertical timing element, the duration expressed in

PCK clock cycles. In this way as with horizontal program-

ming, any pixel rate between 10 and 15 Mpps can be accom-

modated, and any desired standard or non-standard vertical

video timing may be produced.

Like horizontal timing parameters, vertical timing parame-

ters are calculated as follows:

t = N x (PCK period)

= N x (2 x PXCK period)

where N is the value loaded into the appropriate timing reg-

ister, and PCK is the pixel clock period.

The Vertical Interval comprises several different line types

based upon H, the Horizontal line time.

H = (2 x SL) + (2 x SH) [Vertical sync pulses]

= (2 x EL) + (2 x EH) [Equalization pulses]

The VB and VC lines are added to produce the half-lines

needed in the vertical interval at the beginning and end of

some fields. These must properly mate with components of

the normal lines.

VB = CBP + VA - XBP = H/2 – CBPVC

= VA – (EL + EH) = VA – H/2

where Equalization HIGH and LOW pulses (EL + EH) = H/2

and the Extended Color Back Porch, XBP = VA + CBP –VB.

XBP begins after the end of burst, BU, taking the place of

CBP in vertical interval UBV lines. Figure 5 shows the verti-

cal sync and equalization pulse detail

Table 8. Vertical Timing Specifications

Parameter

FP

SY

BR

BU

CBP

VA

H

NTSC-M

(

μ

s)

1.5

4.7

0.6

2.5

1.6

52.6556

63.5556

PAL-I

(

μ

s)

1.65

4.7

0.9

2.25

2.55

51.95

64.0

PAL-M

(

μ

s)

1.9

4.95

0.9

2.25

1.8

51.692

63.492

Parameter

(

μ

s)

H

EH

EL

SH

SL

NTSC-M

(

μ

s)

63.5556

29.4778

2.3

4.7

27.1

PAL-I

(

μ

s)

64

29.65

2.35

4.7

27.3

PAL-M

(

μ

s)

63.492

29.45

2.3

4.65

27.1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC22091R0C | Digital Video Encoders/Layering Engine |

| TMC22191R0C | Digital Video Encoders/Layering Engine |

| TMC22091 | Digital Video Encoders(數(shù)字視頻編碼器) |

| TMC22191 | Digital Video Encoders(數(shù)字視頻編碼器) |

| TMC2242A | Digital Half-Band Interpolating/Decimating Filter 12-bit In/16-bit Out, 60 MHz |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC22191R0C | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22191R0CT | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC222 | 制造商:Trinamic 功能描述:IC SM WITH I2C INTERFACE |

| TMC2220G8A | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC2220G8C | 制造商:Fairchild Semiconductor Corporation 功能描述:CONTROLLER: OTHER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。