- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98256 > TLV5580CDWG4 (TEXAS INSTRUMENTS INC) 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 PDF資料下載

參數(shù)資料

| 型號: | TLV5580CDWG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | GREEN, PLASTIC, SOIC-28 |

| 文件頁數(shù): | 36/36頁 |

| 文件大小: | 478K |

| 代理商: | TLV5580CDWG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁

TLV5580

8BIT, 80 MSPS LOW POWER A/D CONVERTER

SLAS205B DECEMBER 1998 REVISED OCTOBER 2003

www.ti.com

9

ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS WITH FCLK = 80

MSPS AND USE OF EXTERNAL VOLTAGE REFERENCES (unless otherwise noted) (continued)

TIMING REQUIREMENTS

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

fclk

Maximum conversion rate

80

MHz

fclk

Minimum conversion rate

10

kHz

td(o)

Output delay time (see Figure 1)

CL = 10 pF,

See Notes 5 and 6

4.5

9

ns

th(o)

Output hold time

CL = 2 pF,

See Note 5

2

ns

td(pipe)

Pipeline delay (latency)

See Note 6

4.5

CLK

cycles

td(a)

Aperture delay time

3

ns

tj(a)

Aperture jitter

See Note 5

1.5

ps, rms

tdis

Disable time, OE rising to Hi-Z

See Note 5

5

8

ns

ten

Enable, OE falling to valid data

5

8

ns

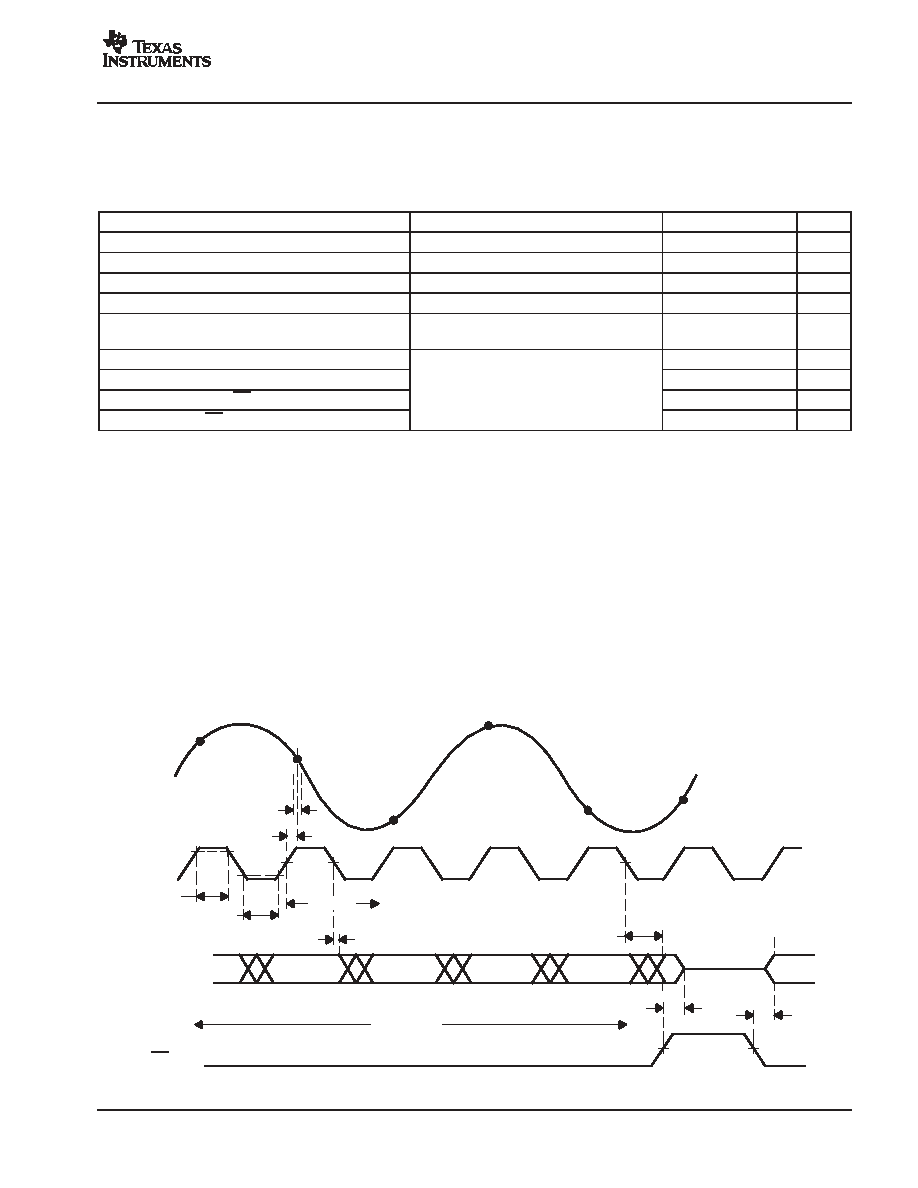

5. Output timing td(o) is measured from the 1.5 V level of the CLK input falling edge to the 10%/90% level of the digital output. The digital output load

is not higher than 10 pF.

Output hold time th(o) is measured from the 1.5 V level of the CLK input falling edge to the 10%/90% level of the digital output. The digital output

is load is not less than 2 pF.

Aperture delay td(A) is measured from the 1.5 V level of the CLK input to the actual sampling instant.

The OE signal is asynchronous.

OE timing tdis is measured from the VIH(MIN) level of OE to the high-impedance state of the output data. The digital output load is not higher than

10 pF.

OE timing ten is measured from the VIL(MAX) level of OE to the instant when the output data reaches VOH(min) or VOL(max) output levels. The digital

output load is not higher than 10 pF.

6. The number of clock cycles between conversion initiation on an input sample and the corresponding output data being made available from the

ADC pipeline. Once the data pipeline is full, new valid output data is provided on every clock cycle. In order to know when data is stable on the

output pins, the output delay time td(o) (i.e., the delay time through the digital output buffers) needs to be added to the pipeline latency. Note that

since the max. td(o) is more than 1/2 clock period at 80 MHz; data cannot be reliably clocked in on a rising edge of CLK at this speed. The falling

edge should be used.

D0D7

N4

N3

N2

N1

N

N+1

N

N+1

N+2

N+3

N+4

N+5

tj(A)

td(A)

VIL

(max)

1.5 V

tw(CLKH)

tw(CLKL)

1/fCLK

th(o)

1.5 V

td(o)

tdis

ten

CLK

OE

90%

10%

VIH(min)

td(pipe)

VOH(min)

VOL(max)

VIL(max)

VIH

(min)

Figure 1. Timing Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV5580CPWG4 | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| TLV5590ED | 1-CH 2-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO14 |

| TLV5590EDR | 1-CH 2-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO14 |

| TLV5592ED | 1-CH 2-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO14 |

| TLV5604CDR | SERIAL INPUT LOADING, 8.5 us SETTLING TIME, 10-BIT DAC, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV5580CDWR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8Bit 80MSPS 1-Ch High Ch Band Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV5580CDWRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8Bit 80MSPS 1-Ch High Ch Band Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV5580CPW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC _ RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV5580CPWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8B 80MSPS ADC Sgl Ch Hi Ch BW Lo Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV5580CPWR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8Bit 80MSPS 1-Ch High Ch Band Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。