- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383949 > TL16C552AMFN (Texas Instruments, Inc.) DUAL ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH FIFO PDF資料下載

參數(shù)資料

| 型號: | TL16C552AMFN |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | DUAL ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH FIFO |

| 中文描述: | 雙異步通信元帶有FIFO |

| 文件頁數(shù): | 19/39頁 |

| 文件大小: | 545K |

| 代理商: | TL16C552AMFN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

TL16C552A, TL16C552AM

DUAL ASYNCHRONOUS COMMUNICATIONS ELEMENT

WITH FIFO

SLLS189D – NOVEMBER 1994 – REVISED JANUARY 1999

19

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

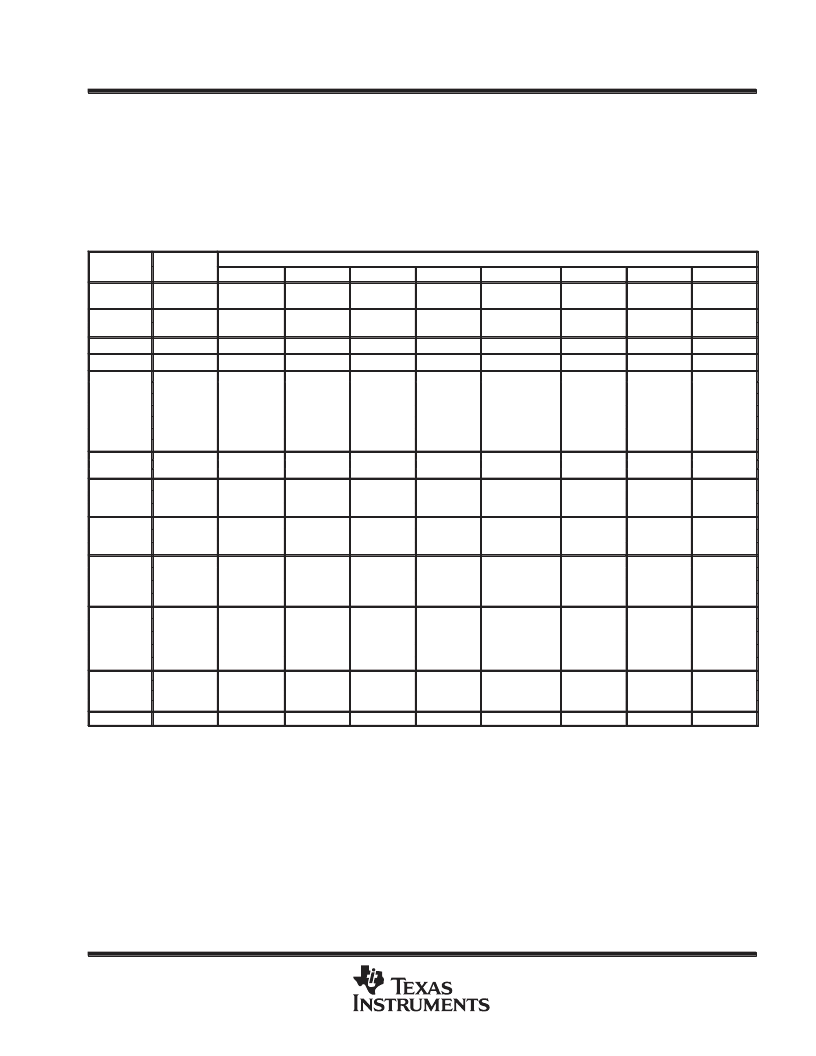

PRINCIPLES OF OPERATION

accessible registers

Using the CPU, the system programmer has access to and control over any of the ACE registers that are

summarized in Table 1. These registers control ACE operations, receive data, and transmit data. Descriptions

of these registers follow Table 3.

Table 3. Summary of Accessible Registers

ADDRESS

REGISTER

MNEMONIC

REGISTER BIT NUMBER

BIT 4

Data Bit 4

BIT 7

Data Bit 7

(MSB)

BIT 6

Data Bit 6

BIT 5

Data Bit 5

BIT 3

Data Bit 3

BIT 2

Data Bit 2

BIT 1

Data Bit 1

BIT 0

Data Bit 0

(LSB)

0

RBR

(read only)

0

THR

Data

Bit 7

Data

Bit 6

Data

Bit 5

Data

Bit 4

Data

Bit 3

Data

Bit 2

Data

Bit 1

Data

Bit 0

(write only)

0

1

1

DLL

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

DLM

IER

Bit 15

0

Bit 14

0

Bit 13

0

Bit 12

0

Bit 11

Bit 10

(ERLSI)

Enable

receiver line

status

interrupt

Bit 9

(ETBEI)

Enable

transmitter

holding

register

empty

interrupt

Receiver

FIFO reset

Bit 8

(ERBFI)

Enable

received

data

available

interrupt

(EDSSI) Enable

modem status

interrupt

2

FCR

Receiver

trigger (MSB)

Receiver

trigger (LSB)

Reserved

Reserved

DMA

Transmitter

FIFO reset

FIFO

enable

(write only)

mode select

2

IIR

FIFOs

enabled

FIFOs

enabled

0

0

Interrupt ID

bit 3

Interrupt ID

bit 2

Interrupt ID

bit 1

0 if

(read only)

interrupt

pending

3

LCR

(DLAB)

Divisor latch

access bit

Set

break

Stick

parity

(EPS)

Even parity

select

(PEN)

(STB)

Number of

stop bits

(WLSB1)

Word length

select bit 1

(WLSB0)

Word length

select bit 0

Parity enable

4

MCR

0

0

0

Loop

OUT2 Enable

external

interrupt

(INT0 or INT1)

OUT1

(an unused

internal

signal)

(RTS)

Request

to send

(DTR)

Data

terminal

ready

5

LSR

Error in

receiver

FIFO

(TEMT)

Transmitter

empty

(THRE)

Transmitter

holding

i t

register

empty

(BI)

Break

interrupt

(FE)

Framing

error

(PE)

Parity

error

(OE)

Overrun

error

(DR)

Data

ready

6

MSR

(DCD)

Data carrier

detect

(RI)

Ring

indicator

(DSR)

Data set

ready

(CTS)

Clear

to send

(

DCD)

Delta data

carrier detect

(TERI)

Trailing edge

ring indicator

(

DSR)

Delta data

set ready

(

CTS)

Delta clear

clear to send

7

SCR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

DLAB = 1

These bits are always 0 when FIFOs are disabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TL16C554AI | ASYNCHRONOUS-COMMUNICATIONS ELEMENT |

| TL16C554I | ASYNCHRONOUS COMMUNICATIONS ELEMENT |

| TL2575-15I | 1-A SIMPLE STEP-DOWN SWITCHING VOLTAGE REGULATORS |

| TL2575-33I | 1-A SIMPLE STEP-DOWN SWITCHING VOLTAGE REGULATORS |

| TL2575_0701 | 1-A SIMPLE STEP-DOWN SWITCHING VOLTAGE REGULATORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TL16C552AMHV | 制造商:Texas Instruments 功能描述:UART 2-CH 16Byte FIFO 5V 68-Pin CFPAK Tube 制造商:Rochester Electronics LLC 功能描述:DUAL 550 UART WITH CENTRONIX PORT - Bulk |

| TL16C552AMHVB | 制造商:Texas Instruments 功能描述:5962-9755001QXA DUAL 550 UART 制造商:Texas Instruments 功能描述:UART 2-CH 16Byte FIFO 5V 68-Pin CFPAK Tube |

| TL16C552AMPN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL ASYNCHRONOUS COMMUNICATIONS ELEMENT WITH FIFO |

| TL16C552APN | 功能描述:UART 接口集成電路 Dual UART w/16-Byte FIFOs & Para Port RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| TL16C552APNG4 | 功能描述:UART 接口集成電路 Dual UART w/ 16-Byte FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。