- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383878 > TAS5028PAGR (Texas Instruments, Inc.) 8 Channel Digital Audio PWM Processor PDF資料下載

參數(shù)資料

| 型號: | TAS5028PAGR |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 8 Channel Digital Audio PWM Processor |

| 中文描述: | 8通道數(shù)字音頻PWM處理器 |

| 文件頁數(shù): | 14/84頁 |

| 文件大?。?/td> | 1051K |

| 代理商: | TAS5028PAGR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

Introduction

6

SLES112 — June 2004

TAS5028

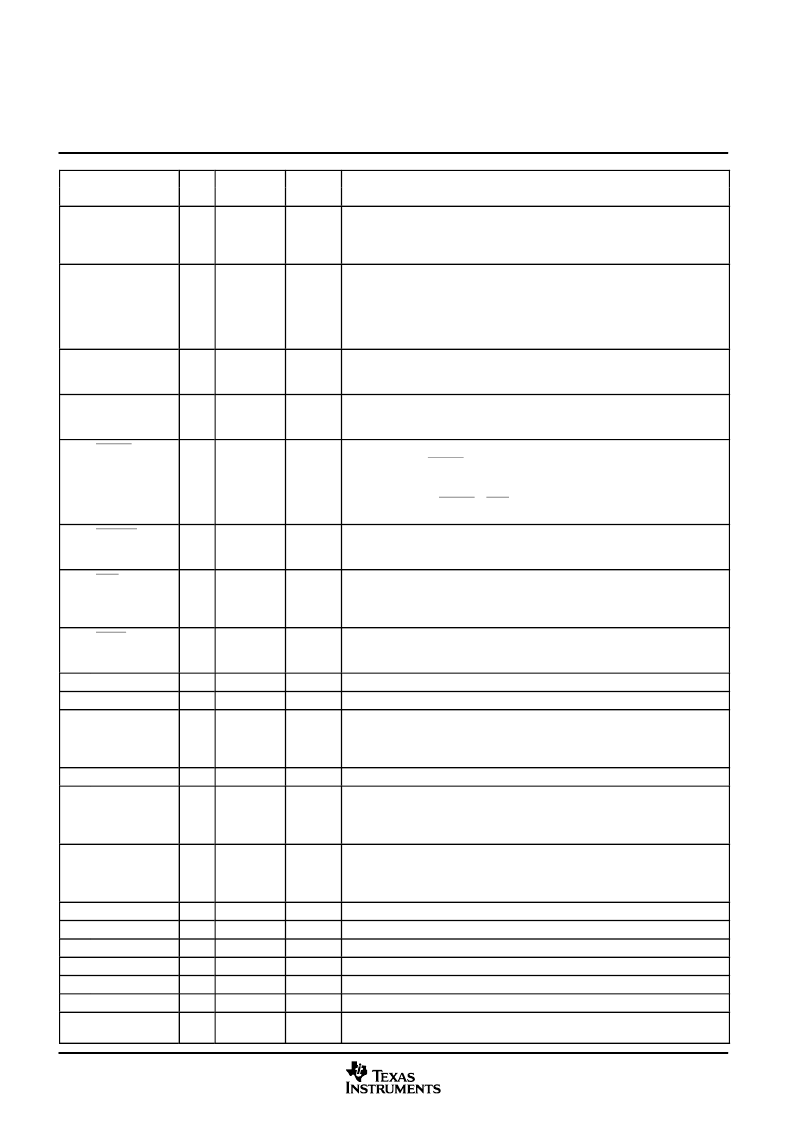

TERMINAL

DESCRIPTION

ATION

5-V

TOLERANT

I/O

NO.

TERMIN-

NAME

7

VRD_PLL

P

Voltage reference for PLL digital supply 1.8 V. A pin-out of the internally regulated

1.8-V power used by PLL logic. A 0.1-

μ

F low ESR capacitor should be connected

between this terminal and AVSS_PLL. This terminal must not be used to power

external devices.

8

AVSS_PLL

P

Analog ground for PLL. This terminal should reference the same ground as power

terminal DVSS, but to achieve low PLL jitter; ground noise at this terminal must be

minimized. The availability of the AVSS terminal allows a designer to use

optimizing techniques such as star ground connections, separate ground planes,

or other quiet ground distribution techniques to achieve a quiet ground reference

at this terminal.

9

AVDD_PLL

P

3.3-V analog power supply for PLL This terminal can be connected to the same

power source used to drive power terminal DVSS, but to achieve low PLL jitter, this

terminal should be bypassed to AVSS_PLL with a 0.1-

μ

F low-ESR capacitor.

10

VBGAP

P

Band gap voltage reference. A pin-out of the internally regulated 1.2-V reference.

Typically has a 1-nF low ESR capacitor between VBGAP and AVSS_PLL. This

terminal must not be used to power external devices.

11

RESET

DI

5 V

Pull up

System reset input, active low. A system reset is generated by applying a logic low

to this terminal. RESET is an asynchronous control signal that restores the

TAS5028 to its default conditions, sets the valid output low, and places the PWM

in the hard mute (M) state. Master volume is immediately set to full attenuation.

Upon the release of RESET, if PDN is high, the system performs a 4-5 ms. device

initialization and set the volume at mute.

12

HP_SEL

DI

5 V

Pull up

Headphone in/out selector. When a logic low is applied, the headphone is selected

(speakers are off). When a logic high is applied, speakers are selected –

headphone is off.

13

PDN

DI

5 V

Pull up

Power down, active low. PDN powers down all logic and stops all clocks whenever

a logic low is applied. The internal parameters are preserved through a power down

cycle, as long as a RESET is not active. The duration for system recovery from

power down is 100 ms.

14

MUTE

DI

5 V

Pull up

Soft mute of outputs, active low (Muted signal = a logic low, normal operation = a

logic high) The mute control provides a noiseless volume ramp to silence.

Releasing mute provides a noiseless ramp to previous volume.

15

DVDD

P

Digital power 3.3-V supply for digital core and most of I/O buffers

16

DVSS

P

Digital ground for digital core and most of I/O buffers

17

VR_DPLL

P

Voltage reference for digital PLL supply 1.8 V. A pin-out of the internally regulated

1.8-V power used by digital PLL logic. A 0.1-

μ

F low ESR capacitor should be

connected between this terminal and DVSS_CORE. This terminal must not be

used to power external devices.

18

OSC_CAP

AO

Oscillator capacitor

19

XTL_OUT

AO

XTL_OUT and XTL_IN are the only LVCMOS terminals on the device. They

provide a reference clock for the TAS5028 via use of an external fundamental mode

crystal. XTL_OUT is the 1.8-V output drive to the crystal. See Note 4 for the

recommended crystal type.

20

XTL_IN

AI

XTL_OUT and XTL_IN are the only LVCMOS terminals on the device. They

provide a reference clock for the TAS5028 via use of an external fundamental mode

crystal. XTL_IN is the 1.8-V input port for the oscillator circuit. See Note 4 for the

recommended crystal type.

21

RESERVED

Connect to digital ground

22

RESERVED

Connect to digital ground

23

RESERVED

Connect to digital ground

I

2

C serial control data interface input / output

I

2

C serial control clock input output

24

SDA

DIO

5 V

25

SCL

DI

5 V

26

LRCLK

DI

5 V

Serial audio data left / right clock (sampling rate clock)

27

SCLK

DI

5 V

Serial audio data clock (shift clock) SCLKIN is the serial audio port (SAP) input data

bit clock that is supplied to the serial bit clock to other I

2

S bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TAS5028PAGRG4 | 8 Channel Digital Audio PWM Processor |

| TAS5036A | Six Channel Digital Audio PWM Processor |

| TAS5036A_06 | Six Channel Digital Audio PWM Processor |

| TAS5036AIPFC | Six Channel Digital Audio PWM Processor |

| TAS5036AIPFCG4 | Six Channel Digital Audio PWM Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TAS5028PAGRG4 | 功能描述:音頻 DSP 8 Ch Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| TAS5036 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SIX CHANNEL DIGITAL AUDIO PWM PROCESSOR |

| TAS5036A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Six Channel Digital Audio PWM Processor |

| TAS5036A_06 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Six Channel Digital Audio PWM Processor |

| TAS5036AIPFC | 功能描述:音頻放大器 Digital Audio PWM Processor RoHS:否 制造商:STMicroelectronics 產(chǎn)品:General Purpose Audio Amplifiers 輸出類型:Digital 輸出功率: THD + 噪聲: 工作電源電壓:3.3 V 電源電流: 最大功率耗散: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。