- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383878 > TAS5010IPFBRG4 (Texas Instruments, Inc.) TRUE DIGITAL AUDIO AMPLIFIER DIGITAL AUDIO PWM PROCESSOR PDF資料下載

參數(shù)資料

| 型號: | TAS5010IPFBRG4 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | TRUE DIGITAL AUDIO AMPLIFIER DIGITAL AUDIO PWM PROCESSOR |

| 中文描述: | 真正的數(shù)字音頻放大器,數(shù)字音頻PWM處理器 |

| 文件頁數(shù): | 7/19頁 |

| 文件大?。?/td> | 268K |

| 代理商: | TAS5010IPFBRG4 |

TAS5010

SLAS328

–

SEPTEMBER 2001

7

www.ti.com

functional description (continued)

reset

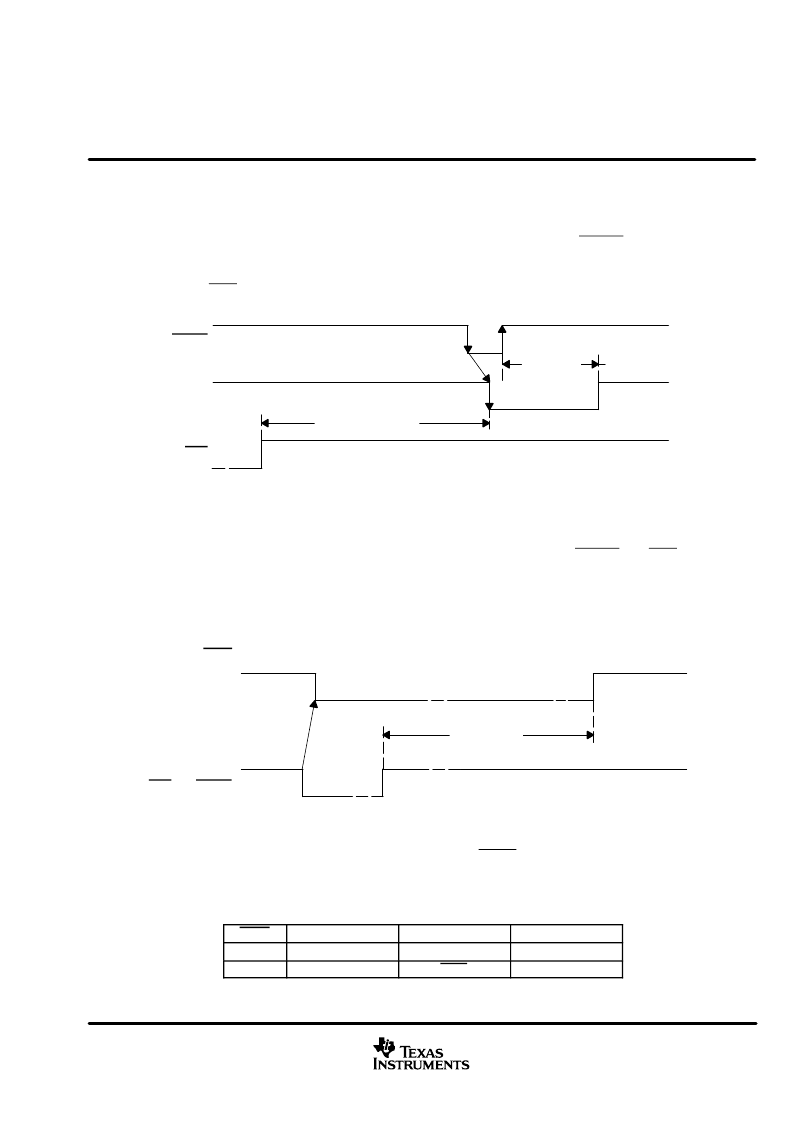

The reset signal for the TAS5010 must be applied whenever toggling the M_S, DBSPD signal. This reset is

asynchronous. See Figure 3 for reset timing. To initiate the reset sequence the RESET pin is asserted low. As

long as the pin is held low the chip is in the reset state. During this reset time the PWM outputs are hard-muted

(P-outputs held low and M-outputs held high) and the PWM outputs valid pins (VALID_L. VALID_R) are held

low. Assuming PDN is high, the rising edge of the reset pulse begins chip initialization. After the initialization

time, the TAS5010 begins normal operation.

Initialization

Normal

Operation

RESET

PDN

Normal Operation

5 ms max

VALID_L

VALID_R

Figure 3. Reset Timing

power down

When PDN is low (see Figure 4), both the PLL and the oscillator are shut down. Note that power down is an

asynchronous operation. To place the device in total power-down mode, both RESET and PDN must be held

low. As long as these pins are held low, the chip is in the power-down state and the PWM outputs are hard muted

with the P outputs held low and the M outputs held high. to place the device back into normal mode, see the

power up section.

NOTE:

In order for the dynamic logic to be properly powered down, the clocks should not be stopped before

the PDN pin goes low. Otherwise, the device may drain additional supply current.

Initialization

Chip

Power-Down

PDN and RESET

Normal Operation

Normal

Operation

VALID

Figure 4. Power-Down Timing

mute

The TAS5010 provides a mute function that is used when the MUTE pin is asserted low. See Table 2 for mute

description. This mute is a quiet mute; that is, the mute is accomplished by outputting a zero value waveform

in which both sides of the differential PWM outputs have a 50% duty cycle (see Figure 5 for mute timing.

Table 2. Mute Description

MUTE

P OUTPUTS

M OUTPUTS

DESCRIPTION

0

50% duty cycle

50% duty cycle

Mute

1

DATA

DATA

Normal operation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TAS5028A | 8 Channel Digital Audio PWM Processor |

| TAS5028APAG | 8 Channel Digital Audio PWM Processor |

| TAS5028APAGG4 | 8 Channel Digital Audio PWM Processor |

| TAS5028APAGR | 8 Channel Digital Audio PWM Processor |

| TAS5028APAGRG4 | 8 Channel Digital Audio PWM Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TAS5010PFB | 功能描述:音頻 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TAS5010PFBG4 | 功能描述:音頻 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TAS5010PFBR | 功能描述:音頻 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TAS5010PFBRG4 | 功能描述:音頻 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TAS5012 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRUE DIGITAL AUDIO AMPLIFIER TAS5012 DIGITAL AUDIO PWM PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。