- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98108 > SN74AVCH2T45YEPR (TEXAS INSTRUMENTS INC) AVC SERIES, 2-BIT TRANSCEIVER, TRUE OUTPUT, PBGA8 PDF資料下載

參數(shù)資料

| 型號: | SN74AVCH2T45YEPR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | AVC SERIES, 2-BIT TRANSCEIVER, TRUE OUTPUT, PBGA8 |

| 封裝: | DSBGA-8 |

| 文件頁數(shù): | 9/22頁 |

| 文件大小: | 365K |

| 代理商: | SN74AVCH2T45YEPR |

www.ti.com

APPLICATION INFORMATION

VCC1

VCC2

SYSTEM-1

SYSTEM-2

1

2

3

4

8

7

6

5

DIR CTRL

I/O-1

VCC2

I/O-2

Enable Times

SN74AVCH2T45

DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVER

WITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTS

SCES582D – JULY 2004 – REVISED AUGUST 2005

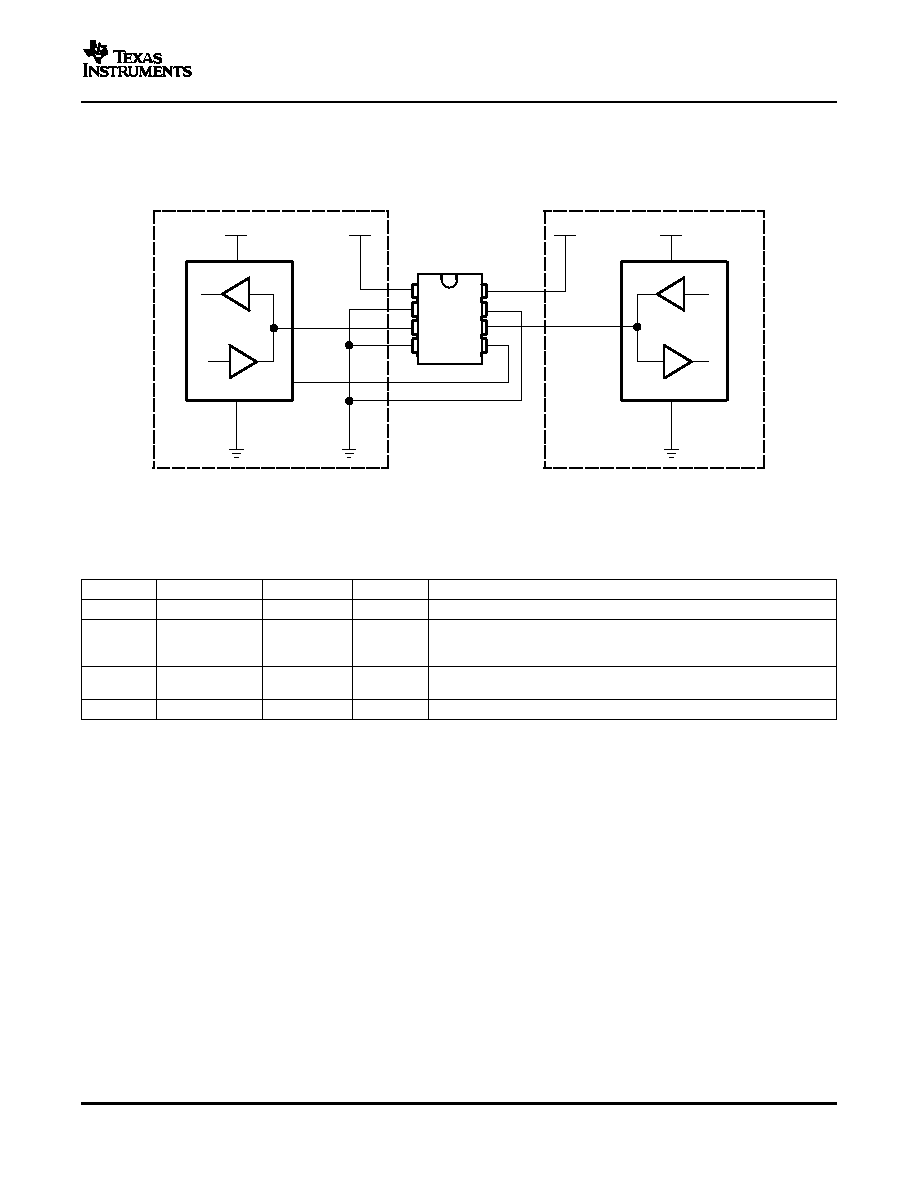

Figure 13 shows the SN74AVCH2T45 used in a bidirectional logic level-shifting application. Since the

SN74AVCH2T45 does not have an output-enable (OE) pin, system designers should take precautions to avoid

bus contention between SYSTEM-1 and SYSTEM-2 when changing directions.

Figure 13. Bidirectional Logic Level-Shifting Application

Following is a sequence that shows data transmission from SYSTEM-1 to SYSTEM-2 and then from SYSTEM-2

to SYSTEM-1.

STATE

DIR CTRL

I/O-1

I/O-2

DESCRIPTION

1

H

Out

In

SYSTEM-1 data to SYSTEM-2

SYSTEM-2 is getting ready to send data to SYSTEM-1. I/O-1 and I/O-2

2

H

Hi-Z

are disabled.

The bus-line state depends on bus hold.

DIR bit is flipped. I/O-1 and I/O-2 still are disabled.

3

L

Hi-Z

The bus-line state depends on bus hold.

4

L

Out

In

SYSTEM-2 data to SYSTEM-1

Calculate the enable times for the SN74AVCH2T45 using the following formulas:

tPZH (DIR to A) = tPLZ (DIR to B) + tPLH (B to A)

tPZL (DIR to A) = tPHZ (DIR to B) + tPHL (B to A)

tPZH (DIR to B) = tPLZ (DIR to A) + tPLH (A to B)

tPZL (DIR to B) = tPHZ (DIR to A) + tPHL (A to B)

In a bidirectional application, these enable times provide the maximum delay from the time the DIR bit is

switched until an output is expected. For example, if the SN74AVCH2T45 initially is transmitting from A to B, the

DIR bit is switched; the B port of the device must be disabled before presenting it with an input. After the B port

has been disabled, an input signal applied to it appears on the corresponding A port after the specified

propagation delay.

17

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74AVCH374DWR | AVC SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| SN74AVCH374DW | AVC SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| SN74AVCH4T245DE4 | AVC SERIES, DUAL 2-BIT TRANSCEIVER, TRUE OUTPUT, PDSO16 |

| SN74AVCH4T245PWR | AVC SERIES, DUAL 2-BIT TRANSCEIVER, TRUE OUTPUT, PDSO16 |

| SN74AVCH8T245DGVR | AVC SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74AVCH2T45YZPR | 功能描述:轉(zhuǎn)換 - 電壓電平 DUAL DUAL SUPPLY BUS TRANSCEIVER RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| SN74AVCH32T245KR | 功能描述:總線收發(fā)器 32B Dual Supply Bus Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74AVCH32T245ZKER | 功能描述:轉(zhuǎn)換 - 電壓電平 32B Dual Supply Bus Transceiver RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| SN74AVCH4T245D | 功能描述:轉(zhuǎn)換 - 電壓電平 4-Bit Dual-Supply Bus Xcvr RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| SN74AVCH4T245DE4 | 功能描述:轉(zhuǎn)換 - 電壓電平 4-Bit Dual-Supply Bus Xcvr RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。