- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384759 > MT8926AE (Mitel Networks Corporation) ISO-CMOS ST-BUS⑩ FAMILY T1 Performance Monitoring Adjunct Circuit (PMAC) PDF資料下載

參數(shù)資料

| 型號(hào): | MT8926AE |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | ISO-CMOS ST-BUS⑩ FAMILY T1 Performance Monitoring Adjunct Circuit (PMAC) |

| 中文描述: | 異意法半導(dǎo)體的CMOS總線⑩家庭T1性能監(jiān)控兼任電路(PMAC下) |

| 文件頁(yè)數(shù): | 9/26頁(yè) |

| 文件大?。?/td> | 309K |

| 代理商: | MT8926AE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)

4-11

MT8926

The MT8926 PMAC can perform a payload loopback

by muxing the data received on the MT8976/77’s

DSTo to DSTi of the MT8976/77. This is controlled by

the MT8926 Loopback Control Word (CSTi1 channel

15, see Table 4).

Figure 6 illustrates the MT8926 payload loopback

connections. The ST-BUS transmit stream (normally

connected to DSTi of the MT8976/77) will connect to

DSTi0 of the MT8926. The DSTo stream of the

MT8976/77 will connect to DSTi1 of the MT8926 and

to the ST-BUS receive stream. DSTo of the MT8926

will connect to DSTi of the MT8976/77.

Line Loopback Codes

T1.403 defines SF mode line loopback activate and

deactivate codes. These codes are either a framed

or un-framed repeating bit sequence of 00001 for

activation or 001 for deactivation. The standard goes

on to say that these codes will persist for five

seconds or more before the loopback action is taken.

The MT8926 will generate line loopback activate and

de-activate codes. These functions are controlled by

the Loopback Control Word of CSTi1 channel 15

(see Table 4). The connections illustrated in Figure 6

must be implemented for this feature to function.

The MT8926 will also detect both framed and un-

framed line loopback activate and de-activate codes

even in the presence of a BER of 3 errors in 1000

bits. See the PMAC Miscellaneous Status Word,

Table 5, CSTo channel 7 bit 3 Line Loopback Enable

Detect (LLED) and bit 4 Line Loopback Disable

Detect (LLDD). The line loopback of T1.403 is

equivalent to the remote loopback function of the

MT8976/77 (see MT8976/77 data sheet, Master

Control Word 2). Therefore, the user will monitor the

LLED and LLDD bits to ensure that they persist for a

minimum of five seconds. Then the line loopback can

be either activated or de-activated using the

MT8976/77 Remote Loopback function.

PMAC Synchronization

The MT8926 has its own frame synchronization

mechanism, which uses the received signal (RxA

and RxB) and E8Ki to achieve SF and ESF frame

and superframe alignment. Further, the PMAC

monitors the SYN bit of the MT8976/77 (CSTo

channel 15 bit 0) and will not declare synchronization

until it is clear. When SYN is low and the MT8926

framer is properly aligned for two superframes, the

PMAC will declare synchronization by making the

Frame Error Count Validation bit (FECV) high. If this

criteria is not met, FECV will be low.

The PMAC will use the received F

T

and F

S

bits, F

T

bits only

or FPS bits to acquire synchronization. The

receive F

T

or FPS bits are used to determine the out-

of-synchronization state (see Table 5).

Timer Outputs

The PMAC has two timer outputs, 1SEC pin and

CSTo TMR bit, which are derived from the 8 kHz ST-

BUS frame pulse F0i. These signals have been

implemented to provide the interface controller with a

timing reference for the transmission of T1.403/408

message-oriented performance data over the FDL.

See the Application section for an explanation of

T1.403/408 FDL Message Transfer.

The 1SEC output (pin 19) changes state once every

half second, and therefore, has a period of one

second. The relationship between the 1SEC output

and the frame pulse F0i is shown in Figure 16.

TMR is bit one of the PMAC Miscellaneous Status

Word (CSTo channel 7, see Table 5). It changes

state once per second on the rising edge of the

1SEC output, and thus, has a two second period.

Therefore, TMR will change state 62 C2i clock cycles

(or ST-BUS bit times) after the frame pulse that

immediately precedes the rising edge of the 1SEC

output.

Framing Error Event Counters

The MT8926 has two four bit counters, the Framing

Error Counter (FE) and the Severely Errored

Framing Event Counter (SE). The FE counter will be

incremented each time a single framing error in the

T1 signal is received. The SE counter will be

incremented by the reception of a T1 framing pattern

with an error rate that is greater than or equal to two

out of six bits. See Table 8 for errored frame event

counter details.

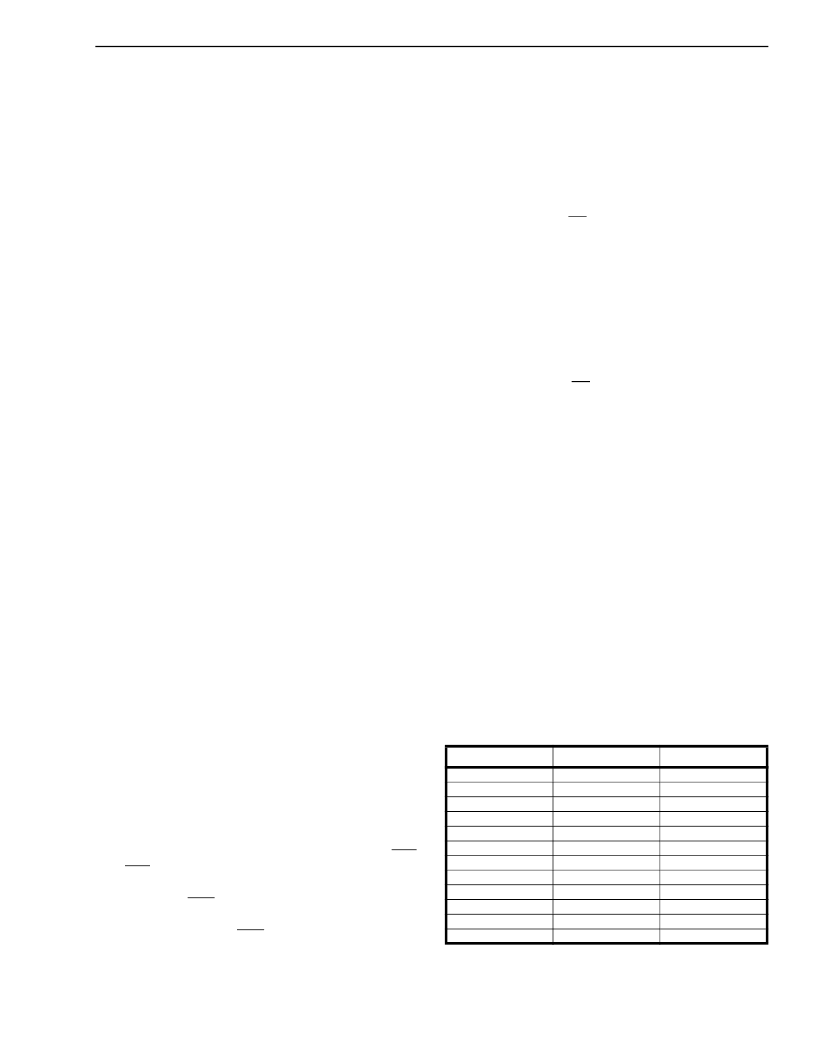

Frame #

F

T

1

1

2

3

0

4

5

1

6

7

0

8

9

1

10

11

0

12

Table 6. D3/D4 or SF Frame Pattern

Table 6 illustrates the Terminal Framing bits (F

T

) and

Signalling Framing bits (F

S

) of the SF or D3/D4

F

S

0

0

1

1

1

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8926AP | ISO-CMOS ST-BUS⑩ FAMILY T1 Performance Monitoring Adjunct Circuit (PMAC) |

| MT8930B | Subscriber Network Interface Circuit |

| MT8930BC | Subscriber Network Interface Circuit |

| MT8930BE | Subscriber Network Interface Circuit |

| MT8930BP | Subscriber Network Interface Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8926AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY T1 Performance Monitoring Adjunct Circuit (PMAC) |

| MT8930 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| MT8930B | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

| MT8930BC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

| MT8930BE | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。