- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384758 > MT8910-1 (Mitel Networks Corporation) CMOS ST-BUS⑩ FAMILY Digital Subscriber Line Interface Circuit PDF資料下載

參數(shù)資料

| 型號: | MT8910-1 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | CMOS ST-BUS⑩ FAMILY Digital Subscriber Line Interface Circuit |

| 中文描述: | 意法半導(dǎo)體的CMOS總線⑩家庭數(shù)字用戶線接口電路 |

| 文件頁數(shù): | 3/26頁 |

| 文件大小: | 419K |

| 代理商: | MT8910-1 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

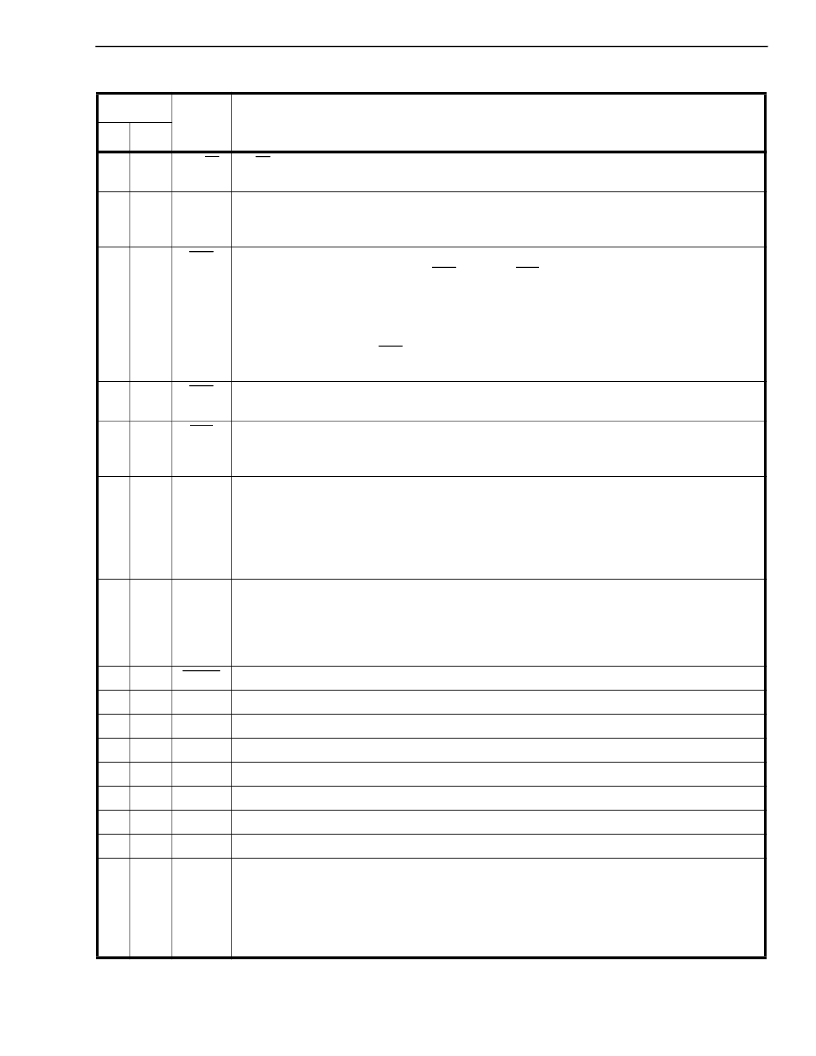

Preliminary Information

MT8910-1

9-5

14

21

NT/LT

NT/LT Mode Select.

CMOS Input. When high, the DSLIC is setup in NT mode. When

low, LT mode is selected.

15

22

TSTen

I/O Structure Test Enable Input.

This active high input enables the built-in test of all

digital input and output structures. Refer to “I/O Structure Test" in functional description for

more details. Tie to V

SS

for normal operation.

Superframe Pulse.

In LT mode, an input pulse once every superframe (12 ms) which,

when low during a falling edge of C4b within an F0b low pulse, sets the transmit

superframe boundary.

16

23

SFb

In NT mode, a 244 ns wide output pulse once every 12 ms indicating the boundary of the

transmit superframe. In NT mode, the superframe timing is generated from the line signal

time base and, as such, SFb will only be valid once the transceiver has achieved full

activation.

17

25

C4b

4096 kHz Data Clock.

In LT mode, a 4096 kHz ST-BUS clock input. In NT mode, a 4096

kHz ST-BUS clock output frequency locked to the line signal.

18

27

F0b

Frame Pulse.

In LT mode, an 8 kHz input pulse indicating the start of the active ST-BUS

channel times. In NT mode, an 8 kHz output pulse extracted from the line signal indicating

the start of the active ST-BUS channel times.

19

30

OSC2

Oscillator Output.

When the MT8910-1 operates with an External Clock (typically LT

mode) connect OSC2 to the output of an external inverter providing a 10.24 MHz ±5ppm

clock (see “10.24 MHz Clock Interface" section).

When operating with a crystal (typically NT mode) connect one lead of the fundamental

mode parallel resonator crystal (10.24 MHz ±50ppm in case of NT mode).

20

31

OSC1

Oscillator Input.

When the DSLIC operates with an External Clock (typically LT mode)

connect OSC1 to the input of an external inverter (see Fig.11).

When operating with a crystal (typically NT mode) connect the other lead of the

fundamental mode parallel resonator crystal (10.24 MHz ±50ppm in case of NT mode).

21

32

MRST

Master Reset.

Active low CMOS input performs a master reset of the DSLIC.

22

33

V

DD

IC

Power Supply Input.

23

34

Internal Connection.

Leave unconnected.

24

38

AV

DD

V

Bias

V

Ref

L

in-

L

in+

NC

Analog Power Supply.

Connect to V

DD

.

Bias Voltage.

Decouple to AV

SS

through a 1.0 μF ceramic capacitor.

Reference Voltage.

Decouple to AV

SS

through a 1.0 μF ceramic capacitor.

Line Signal Input Minus.

Internally biased at V

Bias.

Line Signal Input Plus.

Internally biased at V

Bias.

No Connection.

Leave circuit open.

25

41

26

42

27

43

28

44

2,4,7,

9 -11,

17,24

26,28

29,35

36,37

39,40

Pin Description (continued)

Pin #

Name

Description

DIP PLCC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8910-1AC | CMOS ST-BUS⑩ FAMILY Digital Subscriber Line Interface Circuit |

| MT8910-1AP | CMOS ST-BUS⑩ FAMILY Digital Subscriber Line Interface Circuit |

| MT8920 | ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

| MT8920B | ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

| MT8920B-1 | ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8910-1AC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Digital Subscriber Line Interface Circuit |

| MT8910-1AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:CMOS ST-BUS⑩ FAMILY Digital Subscriber Line Interface Circuit |

| MT8920 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

| MT8920AE | 制造商:Mitel Networks Corporation 功能描述: |

| MT8920B | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。