- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359228 > MT312 (ZARLINK SEMICONDUCTOR INC) Satellite Channel Decoder PDF資料下載

參數(shù)資料

| 型號: | MT312 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 消費家電 |

| 英文描述: | Satellite Channel Decoder |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | MQFP-80 |

| 文件頁數(shù): | 20/90頁 |

| 文件大小: | 318K |

| 代理商: | MT312 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

MT312

Initialisation

20

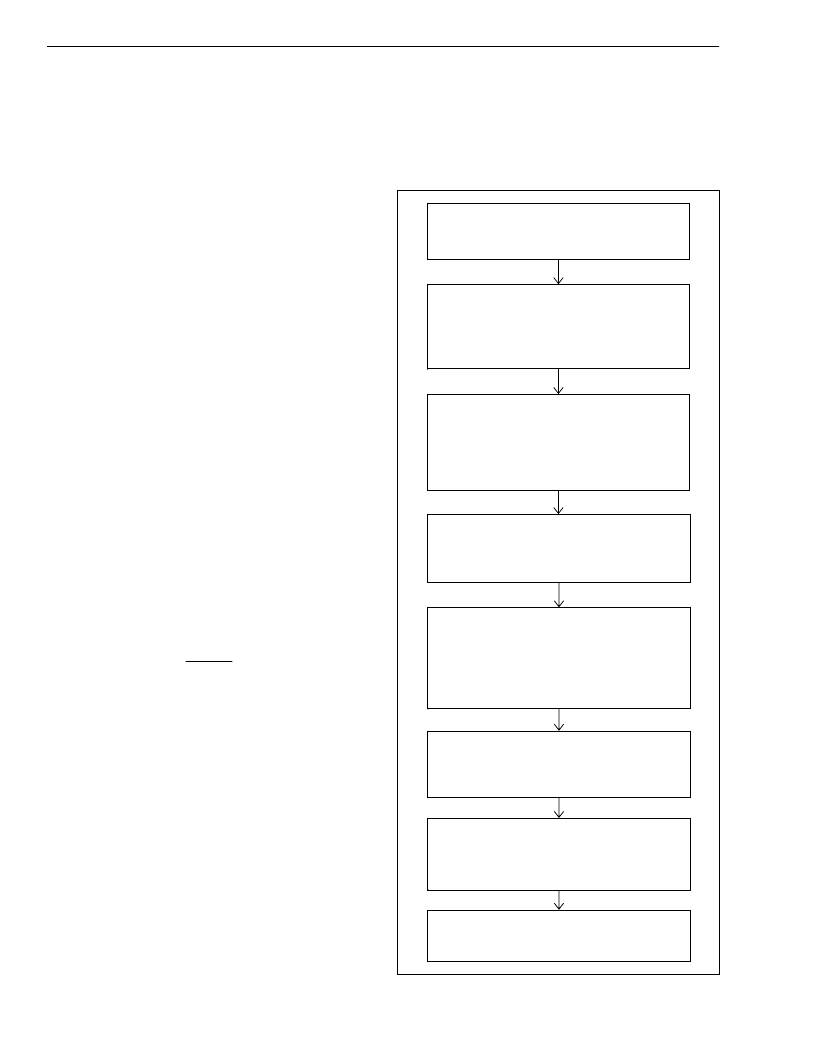

3.3 Initialisation Sequence

MT312 will be in the power save mode after a

hardware reset. The

fi

rst command to be written

must be to the CONFIGURATION register at address

127. After loading this register, wait 150μs before

writing to the RESET register. During this wait, the

tuner can programmed to the required channel

frequency via the General Purpose Port (register

20). If the AGC slope control bit of AGC CTRL(39) or

the AGC REF(41) are to be changed, it is best to

write to these registers after writing to the RESET

register. This will allow the front-end AGC loop to

settle while the other registers are being written.

Next write 128 to the RESET register (21) to reset

the MT312 state machine and all parameter registers

to the default settings. It is then necessary to change

the default setting of register 49 to 50 (decimal).

If necessary, other default parameters may need to

be changed. These may include:

Slope of AGC control signal - see register (39)

ACG CTRL[B0] AGC SL bit

AGC Reference value - see register (41) AGC

REF

Relative phase of IQ spectrum - see register

(25) VIT MODE[B6]

LNB frequency search range, default is ±6MHz

- see register (37) FR LIM

For low Baud rates only, set fast frequency

acquisition mode - see register (26) set QPSK

CTRL[B2] = 1

To invert MOCLK or BKERR output signals - see

register (96) OP CTRL

After this, the LNB controls are de

fi

ned, in register

(22) DISEQC MODE.

The signal parameters should then be written to the

MT312. The symbol rate (registers 23 & 25 SYM

RATE) may be speci

fi

ed within ±2% of the required

value, absolute precision is not required to achieve

successful lock and tracking. If the symbol rate is

unknown, a search mode is available.

Selecting the correct bit of register (25) VIT MODE, if

known, programs the convolutional code rate. If the

code rate is unknown, some or all of the bits of VIT

MODE may be set to force the MT312 to search for

the code rate.

Finally, the MT312 is given a GO command, register

(27) GO =1, to release the state machine and to start

the signal acquisition sequence. This is summarised

as an example in the following

fl

ow diagram.

Enable MT312 : Program CONFIG

Reg 127 = 140 (8Chex)

Program tuner via GPP in 'pass through mode'

open port with Reg 20 = 64 (40hex)

send TUNER DATA via I2C bus (5 bytes).

close port with Reg 20 = 0

Reset MT312 to default register settings

Reg21 = 128 (80hex)

Set SYS_CLK = 2*Xtal*PLL_RATIO

Set DISEQQC_RATIO (if required)

Set AGC_SL (if required)

Initialise register: reg 49 = 50 (32hex);

DiSEqC mode

eg Horizontal with 22kHz on:

Reg 22 = 65 (41hex)

Signal input - Symbol rate

eg 27.5 MBaud:

Reg 23 = 27 (1Bhex) DEFAULT state

Reg 24 = 128 (80hex) DEFAULT state

Viterbi code rate

eg V_IQ swap not set, CR = 3/4:

Reg 25 = 4 (4hex)

QPSK control

eg DVB : roll-off = 0.35:

Reg 26 = 0 DEFAULT state

GO

Release reset state to start signal capture

Reg 27 = 1

Figure 15 - Initialisation sequence in DVB mode

相關PDF資料 |

PDF描述 |

|---|---|

| MT312T-Y | 2x4mm Rectangular LED Lamps |

| MT3371BN | Wide Dynamic Range DTMF Receiver |

| MT3371BS | Wide Dynamic Range DTMF Receiver |

| MT3371BNR | Wide Dynamic Range DTMF Receiver |

| MT3371BSR1 | Wide Dynamic Range DTMF Receiver |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT3-1203SI | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:3 WATT DC/DC CONVERTER, SIINGLE & MULTIIPLE OUTPUTS |

| MT3-1205SI | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:3 WATT DC/DC CONVERTER, SIINGLE & MULTIIPLE OUTPUTS |

| MT3-1212SI | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:3 WATT DC/DC CONVERTER, SIINGLE & MULTIIPLE OUTPUTS |

| MT3-1212WI | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:3 WATT DC/DC CONVERTER, SIINGLE & MULTIIPLE OUTPUTS |

| MT3-1215WI | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:3 WATT DC/DC CONVERTER, SIINGLE & MULTIIPLE OUTPUTS |

發(fā)布緊急采購,3分鐘左右您將得到回復。