- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98023 > MK50N512CLL100R (FREESCALE SEMICONDUCTOR INC) 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | MK50N512CLL100R |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, LQFP-100 |

| 文件頁數(shù): | 48/73頁 |

| 文件大小: | 1829K |

| 代理商: | MK50N512CLL100R |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

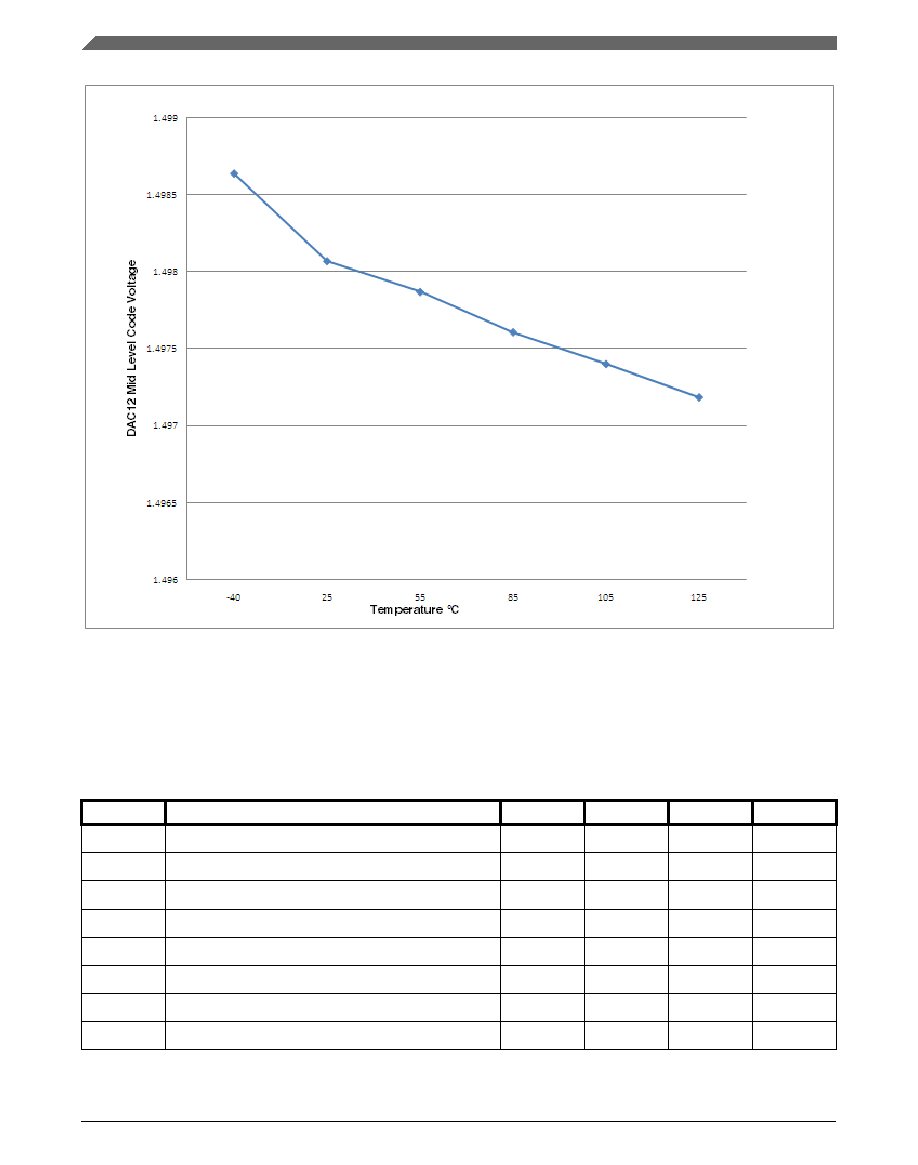

Figure 19. Offset at half scale vs. temperature

6.6.4 Op-amp electrical specifications

Table 31. Op-amp electrical specifications

Symbol

Description

Min.

Typ.

Max.

Unit

VDD

Operating voltage

1.71

—

3.6

V

ISUPPLY

Supply current (IOUT=0mA, CL=0), low-power mode

—

70

TBD

μA

ISUPPLY

Supply current (IOUT=0mA, CL=0), high-speed mode

—

500

TBD

μA

VOS

Input offset voltage

—

±3

TBD

mV

αVOS

Input offset voltage temperature coefficient

—

10

—

μV/C

IOS

Input offset current (0~50°C)

—

±300

—

pA

IOS

Input offset current (-40~105°C)

—

TBD

—

pA

IBIAS

Input bias current (0~50°C)

—

±300

—

pA

Table continues on the next page...

Peripheral operating requirements and behaviors

K50 Sub-Family Data Sheet Data Sheet, Rev. 4, 3/2011.

52

Preliminary

Freescale Semiconductor, Inc.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MK50X256CLL100 | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP100 |

| MK50N512CLL100 | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP100 |

| ML53812-2 | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP176 |

| ML54051 | FLASH MEMORY DRIVE CONTROLLER, PQFP120 |

| ML60851CGA | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MK50N512CLQ100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK50N512CMC100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK50N512CMD100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK50X256CLK100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

| MK50X256CLL100 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。