- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369901 > MC44460B (MOTOROLA INC) PICTURE-IN-PICTURE (PIP) CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | MC44460B |

| 廠商: | MOTOROLA INC |

| 元件分類: | 畫面疊加 |

| 英文描述: | PICTURE-IN-PICTURE (PIP) CONTROLLER |

| 中文描述: | PICTURE-IN-PICTURE IC, PDIP56 |

| 封裝: | SHRINK, PLASTIC, DIP-56 |

| 文件頁數(shù): | 11/16頁 |

| 文件大小: | 439K |

| 代理商: | MC44460B |

MC44460

11

MOTOROLA ANALOG IC DEVICE DATA

to prevent the PIP from interfering with the main picture

sync pulses.

PIP Y Position Register

Sub–address = 07h

Y Position Bits (YPS0–5) – D0–D5

Moves the PIP start position from the top to the bottom

edge of the display in 64 steps. There is protection circuitry to

prevent the PIP from interfering with the main picture sync

pulses.

PIP Chroma Level Register

Sub–address = 08h

Chroma (C0–5) – D0–D5

The color of the PIP can be adjusted to suit viewer

preference by setting the value stored in these bits. A total of

64 steps varies the color from no color to maximum. This

control acts in conjunction with the auto phase control.

PIP Tint Level Register

Sub–address = 09h

Tint (T0–5) – D0–D5

An auto phase control compares the main color burst to

are matched. In addition to this, the tint of the PIP can be

varied

±

10

°

in a total of 64 steps by changing the value of

these bits to suit viewer preference.

PIP Luma Delay Register

Sub–address = 0Ah

Y Delay (YDL0–2) – D0–D2

Since the Chroma passes through a bandpass filter and

the color decoder, it is delayed with respect to the Luma

signal. Therefore, to time match the Luma and Chroma these

bits are set to a single value determined to be correct in the

application.

Pip Fill/Test Register

Sub–address = 0Ch

PIP Fill Bits (PIPFILL0–1) – D0–D1

May be used to fill the PIP with one of three selectable

solid colors

Test Register Bits (INTC0 and MACR0) – D6–D7

Used for production test only.

áááááááááááááááááááááááááááááááááá

áááááááááááááááááááááááááááááááááá

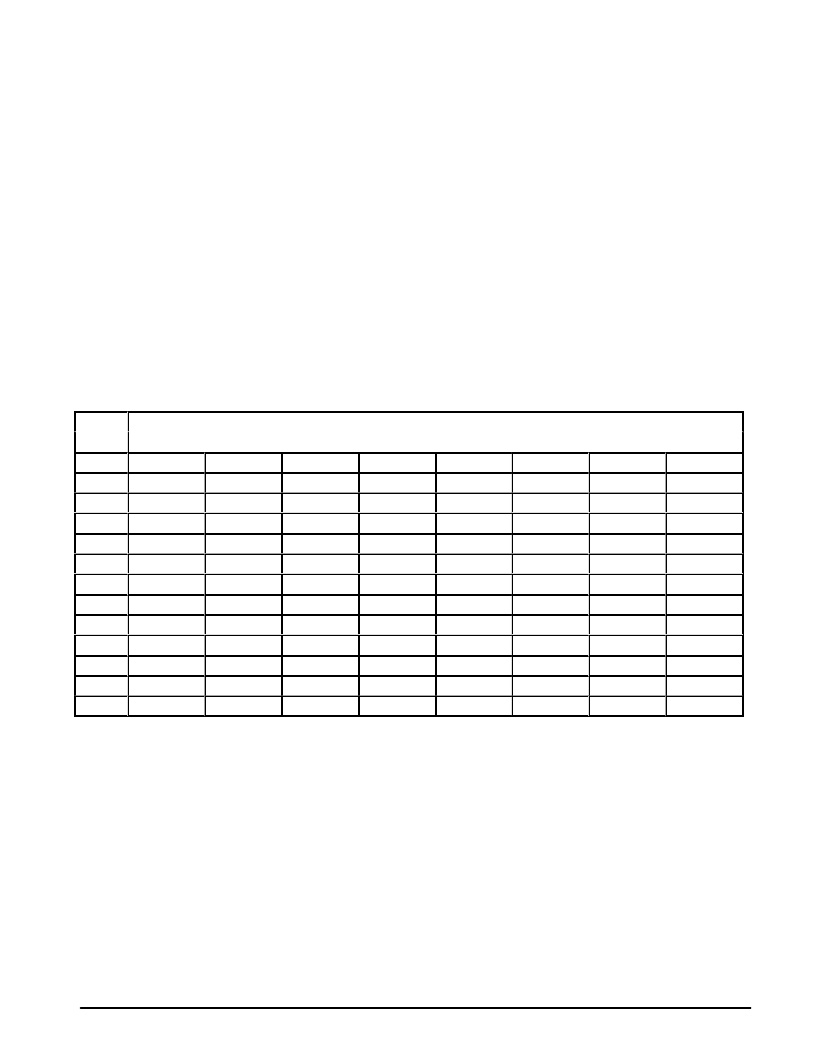

I2C REGISTER TABLE

áááááááááááááááááááááááááááááááááá

áááááááááááááááááááááááááááááááááá

address

D7

D6

D5

D4

áááá

Data Bit

ááááááááááááááááááááááááááááááá

00

áááá

RPS3

áááá

RPS2

ááááá

RPS1

ááááá

RPS0

ááááá

–

áááá

D3

WPS2

ááááá

D2

D1

WPS1

ááááá

D0

WPS0

ááááá

01

áááá

–

áááá

ááááá

–

ááááá

VFON

ááááá

PSD3

áááá

PSD2

ááááá

PSD1

ááááá

PSD0

ááááá

02

áááááááááááááááááááááááááááááááááá

03

–

MHP0

MVP0

–

–

–

–

–

–

–

BC2

ITM2

BC1

ITM1

BC0

ITM0

04

PSEL0

MSEL0

–

PSI90

STIL0

–

ááááá

–

–

05

–

ááááá

–

PBL0

–

ááááá

–

PON0

06

–

ááááá

XPS5

XPS4

XPS3

XPS2

–

XPS1

XPS0

áááá

07

áááá

–

ááááá

ááááá

–

ááááá

YPS5

ááááá

YPS4

áááá

YPS3

YPS2

–

ááááá

YPS1

ááááá

YPS0

áááá

08

áááá

–

ááááá

–

ááááá

C5

ááááá

C4

áááá

C3

ááááá

ááááá

C1

ááááá

C0

áááá

09

áááá

–

ááááá

–

ááááá

T5

ááááá

T4

áááá

T3

ááááá

ááááá

ááááá

T1

ááááá

T0

áááá

0A

áááá

–

ááááá

–

ááááá

–

ááááá

–

áááá

–

ááááá

YDL2

C2

ááááá

YDL1

ááááá

YDL0

áááá

0B

áááá

–

ááááá

–

ááááá

–

ááááá

–

áááá

–

ááááá

T2

ááááá

–

ááááá

–

áááá

áááá

–

ááááá

ááááá

áááá

ááááá

ááááá

áááá

áááá

0C

áááá

áááá

–

ááááá

–

ááááá

ááááá

–

ááááá

ááááá

–

áááá

áááá

–

ááááá

ááááá

–

ááááá

ááááá

–

ááááá

ááááá

–

áááá

áááá

áááá

áááá

ááááá

–

ááááá

ááááá

ááááá

ááááá

áááá

áááá

ááááá

–

ááááá

ááááá

ááááá

ááááá

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC44460 | PICTURE-IN-PICTURE (PIP) CONTROLLER |

| MC44461B | RV Series - Econoline Unregulated DC-DC Converters; Input Voltage (Vdc): 24V; Output Voltage (Vdc): 05V; Power: 2W; High Isolation 2W Converter; Approved for Medical Applications; EN and UL Safety Certificates; 6kVDC Isolation; Skinny DIP24 Package; Optional Continuous Short Circuit Protected; Fully Encapsulated; Very Low Isolation Capacitance |

| MC44461 | PICTURE-IN-PICTURE (PIP) CONTROLLER |

| MC44462B | Y-C PICTURE-IN-PICTURE (PIP) CONTROLLER |

| MC44462 | Y-C PICTURE-IN-PICTURE (PIP) CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC44461 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PICTURE-IN-PICTURE (PIP) CONTROLLER |

| MC44461B | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PICTURE-IN-PICTURE (PIP) CONTROLLER |

| MC44462 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Y-C PICTURE-IN-PICTURE (PIP) CONTROLLER |

| MC44462B | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Y-C PICTURE-IN-PICTURE (PIP) CONTROLLER |

| MC44463 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:REPLAY AND MULTIPLE PICTURE-IN-PICTURE (PIP) CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。