- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384641 > M5M44405CTP-6S (Mitsubishi Electric Corporation) EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號: | M5M44405CTP-6S |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

| 中文描述: | 江戶(超頁模式)4194304位(1048576 - Word的4位)動態(tài)隨機存儲器 |

| 文件頁數(shù): | 4/27頁 |

| 文件大?。?/td> | 244K |

| 代理商: | M5M44405CTP-6S |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM

M5M44405CJ,TP-5,-6,-7,-5S,-6S,-7S

MITSUBISHI LSIs

M5M44405CJ,TP-5,-5S:Under development

Note 6 : An initial pause of 200μs is required after power-up followed by a minimum of eight initialization cycles (RAS only refresh or CAS before RAS refresh

cycles).

Note the RAS may be cycled during the initial pause . And eight initialization cycles are required after prolonged periods (greater than

t

REF(max)

) of RAS

inactivity before proper device operation is achieved.

Note

7 : Measured with a load circuit equivalent to 2TTL and 100pF.

The reference levels for measuring of output signals are 2.0V(V

OH

) and 0.8V(V

OL

).

Note

8 : Assumes that

t

RCD

≥

t

RCD(max)

and

t

ASC

≥

t

ASC(max)

and

t

CP

≥

t

CP(max)

.

Note

9 : Assumes that

t

RCD

≤

t

RCD(max)

and

t

RAD

≤

t

RAD(max)

. If

t

RCD

or

t

RAD

is greater than the maximum recommended value shown in this table,

t

RAC

will

increase by amount that

t

RCD

exceeds the value shown.

Not

10 : Assumes that

t

RAD

≥

t

RAD(max)

and

t

ASC

≤

t

ASC(max)

.

No t

11 : Assumes that

t

CP

≤

t

CP(max)

and

t

ASC

≥

t

ASC(max)

.

No t

12 :

t

OEZ(max)

,

t

WEZ(max)

,

t

OFF(max)

and

t

REZ(max)

defines the time at which the output achieves the high impedance state (I

OUT

≤

±10μA ) and is not

reference to V

OH(min)

or V

OL(max)

.

Not

13 : Output is disabled after both RAS and CAS go to high.

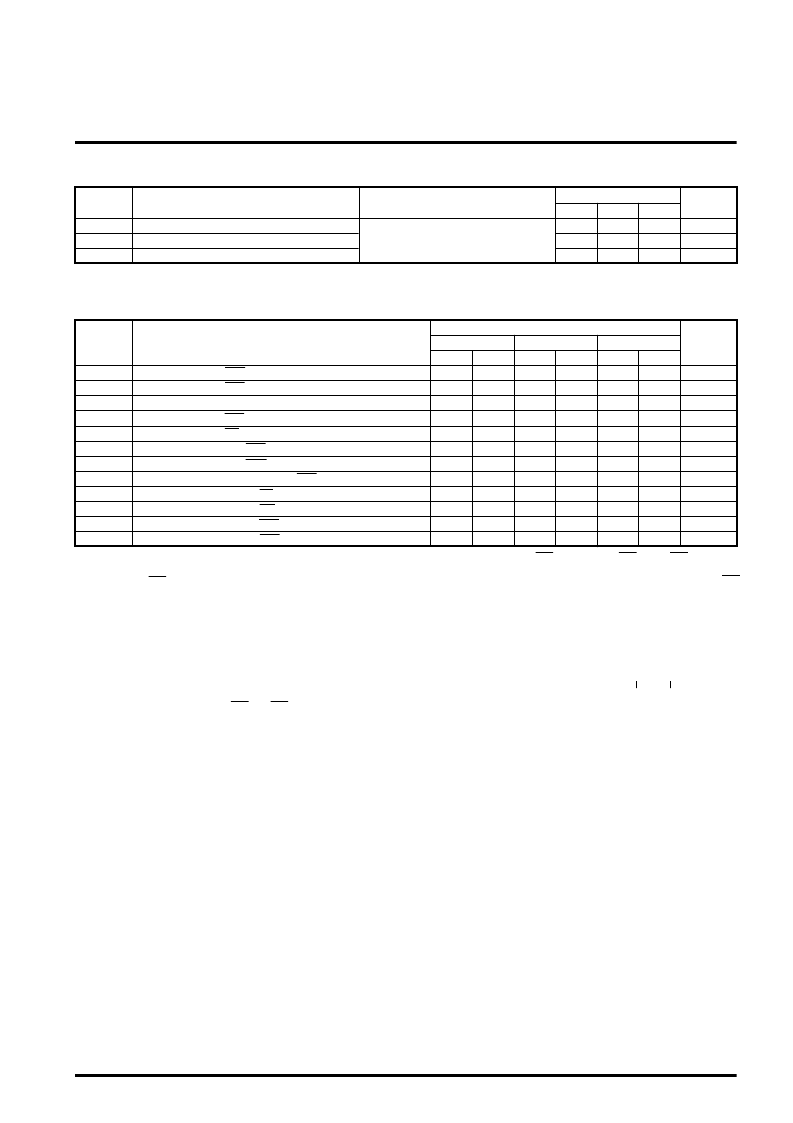

CAPACITANCE

(Ta=0~70C, V

CC

= 5V±10%, V

SS

=0V, unless otherwise noted)

pF

pF

pF

C

I (A)

C

I (CLK)

C

I / O

5

7

7

V

I

=V

SS

f=1MHz

V

I

=25mVrms

SWITCHING CHARACTERISTICS

(Ta=0~70C, V

CC

= 5V±10%, V

SS

=0V, unless otherwise noted, see notes 6,14,15)

t

CAC

t

RAC

t

AA

t

CPA

t

OEA

t

OHC

t

OHR

t

CLZ

t

OEZ

t

WEZ

t

OFF

t

REZ

ns

ns

ns

ns

ns

30

33

15

60

25

28

13

50

35

38

20

70

5

5

15

15

13

13

ns

ns

ns

ns

ns

13

13

15

15

5

20

20

20

20

ns

15

13

20

M5M44405C-5,-5S M5M44405C-6,-6S M5M44405C-7,-7S

Min

Max

Min

5

5

ns

5

5

5

5

4

Limits

Typ

Min

Max

Unit

Symbol

Parameter

Test conditions

Parameter

Symbol

Limits

Unit

Max

Min

Max

Input capacitance, address inputs

Input capacitance, clock inputs

Input/Output capacitance, data ports

Access time from CAS

Access time from RAS

Column address access time

Access time from CAS precharge

Access time from OE

Output hold time from CAS

Output hold time from RAS

(Note 7,8)

(Note 7,9)

(Note 7,10)

(Note 7,11)

(Note 7)

(Note 12)

(Note 12)

(Note 12,13)

(Note 12,13)

Output disable time after OE high

Output disable time after WE high

Output disable time after CAS high

Output disable time after RAS high

Output low impedance time from CAS low

(Note 7)

(Note 13)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M44405CTP-7 | EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

| M5M44405CTP-7S | EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

| M5M44405CJ-7 | EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

| M5M44405CJ-7S | EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

| M5M44405CJ-5 | EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M44405CTP-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

| M5M44405CTP-7S | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO ( HYPER PAGE MODE ) 4194304-BIT ( 1048576-WORD BY 4-BIT ) DYNAMIC RAM |

| M5M4454AP | 制造商:MITSU 功能描述: |

| M5M4464AJ10 | 制造商:MITSUBISHI 功能描述:* |

| M5M4464AL-12 | 制造商:Mitsubishi Electric 功能描述: 制造商:MITSU 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。