- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224146 > M470T6464EHS-LF7 DDR DRAM MODULE, ZMA200 PDF資料下載

參數(shù)資料

| 型號: | M470T6464EHS-LF7 |

| 元件分類: | DRAM |

| 英文描述: | DDR DRAM MODULE, ZMA200 |

| 封裝: | ROHS COMPLIANT, SODIMM-200 |

| 文件頁數(shù): | 17/22頁 |

| 文件大?。?/td> | 401K |

| 代理商: | M470T6464EHS-LF7 |

Rev. 1.0 August 2008

SODIMM

DDR2 SDRAM

4 of 22

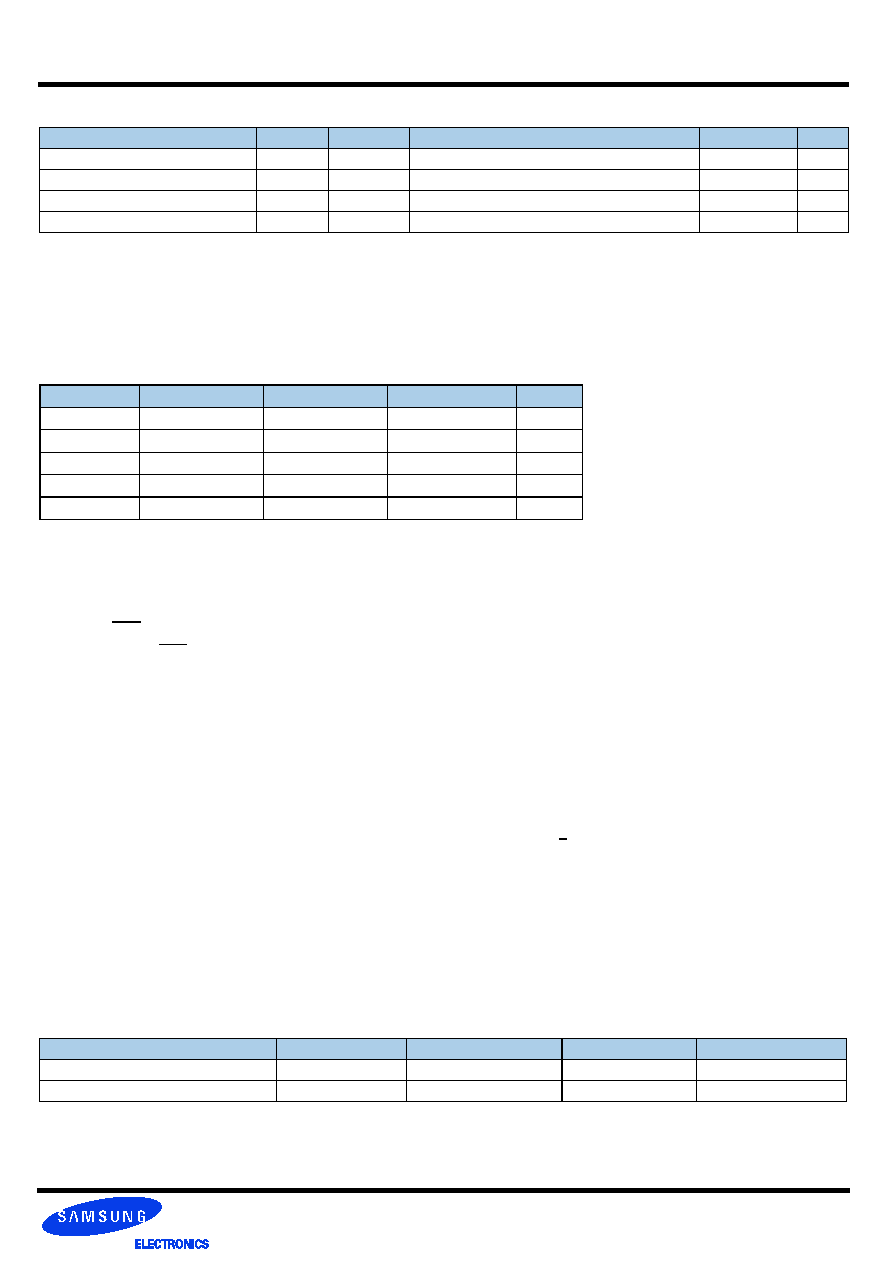

1.0 DDR2 Unbuffered SODIMM Ordering Information

2.0 Features

Note :

1. “H” of Part number(12th digit) stands for Lead-Free, Halogen-Free, and RoHS compliant products.

2. “3” of Part number(13th digit) stands for Dummy Pad PCB products.

Part Number

Density

Organization

Component Composition

Number of Rank Height

M470T5663EH3-C(L)E7/F7/E6

2GB

256Mx64

128Mx8(K4T1G084QE-HC(L)E7/F7/E6)*16

2

30mm

M470T2864EH3-C(L)E7/F7/E6

1GB

128Mx64

64Mx16(K4T1G164QE-HC(L)E7/F7/E6)*8

2

30mm

M470T2863EH3-C(L)E7/F7/E6

1GB

128Mx64

128Mx8(K4T1G084QE-HC(L)E7/F7/E6)*8

1

30mm

M470T6464EHS-C(L)E7/F7/E6

512MB

64Mx64

64Mx16(K4T1G164QE-HC(L)E7/F7/E6)*4

1

30mm

Performance range

JEDEC standard VDD = 1.8V ± 0.1V Power Supply

VDDQ = 1.8V ± 0.1V

333MHz fCK for 667Mb/sec/pin, 400MHz fCK for 800Mb/sec/pin

8 Banks

Posted CAS

Programmable CAS Latency: 3, 4, 5, 6

Programmable Additive Latency: 0, 1 , 2 , 3, 4, 5

Write Latency(WL) = Read Latency(RL) -1

Burst Length: 4 , 8(Interleave/Nibble sequential)

Programmable Sequential / Interleave Burst Mode

Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional feature)

Off-Chip Driver(OCD) Impedance Adjustment

On Die Termination with selectable values(50/75/150 ohms or disable)

Average Refresh Period 7.8us at lower than a TCASE 85°C, 3.9us at 85°C < TCASE < 95 °C

- Support High Temperature Self-Refresh rate enable feature

Package: 60ball FBGA - 128Mx8 and 84ball FBGA - 64Mx16

All of base components are Lead-Free, Halogen-Free, and RoHS compliant

Note : For detailed DDR2 SDRAM operation, please refer to Samsung’s Device operation & Timing diagram.

E7 (DDR2-800)

F7 (DDR2-800)

E6 (DDR2-667)

Unit

Speed@CL3

400

-

400

Mbps

Speed@CL4

533

Mbps

Speed@CL5

800

667

Mbps

Speed@CL6

-

800

-Mbps

CL-tRCD-tRP

5-5-5

6-6-6

5-5-5

CK

3.0 Address Configuration

Organization

Row Address

Column Address

Bank Address

Auto Precharge

128Mx8(1Gb) based Module

A0-A13

A0-A9

BA0-BA2

A10

64Mx16(1Gb) based Module

A0-A12

A0-A9

BA0-BA2

A10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48T128V | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T12 | 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM |

| M48T12-150PC1 | 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM |

| M48T12-200PC1 | 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM |

| M48T12-70PC1 | 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M470T6464QZH3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR2 SDRAM Memory |

| M470T6554BG0-CD5/CC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:200pin Unbuffered SODIMM based on 512Mb B-die 64bit Non-ECC |

| M470T6554BG3-CD5/CC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:200pin Unbuffered SODIMM based on 512Mb B-die 64bit Non-ECC |

| M470T6554BGZ0-CD5/CC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:200pin Unbuffered SODIMM based on 512Mb B-die 64bit Non-ECC |

| M470T6554BGZ3-CD5/CC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:200pin Unbuffered SODIMM based on 512Mb B-die 64bit Non-ECC |

發(fā)布緊急采購,3分鐘左右您將得到回復。