- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180205 > M393B5273CH0-CK0 512M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 PDF資料下載

參數(shù)資料

| 型號: | M393B5273CH0-CK0 |

| 元件分類: | DRAM |

| 英文描述: | 512M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 |

| 封裝: | HALOGEN FREE AND ROHS COMPLIANT, DIMM-240 |

| 文件頁數(shù): | 37/58頁 |

| 文件大小: | 1982K |

| 代理商: | M393B5273CH0-CK0 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

- 35 -

datasheet

DDR3 SDRAM

Rev. 1.0

Registered DIMM

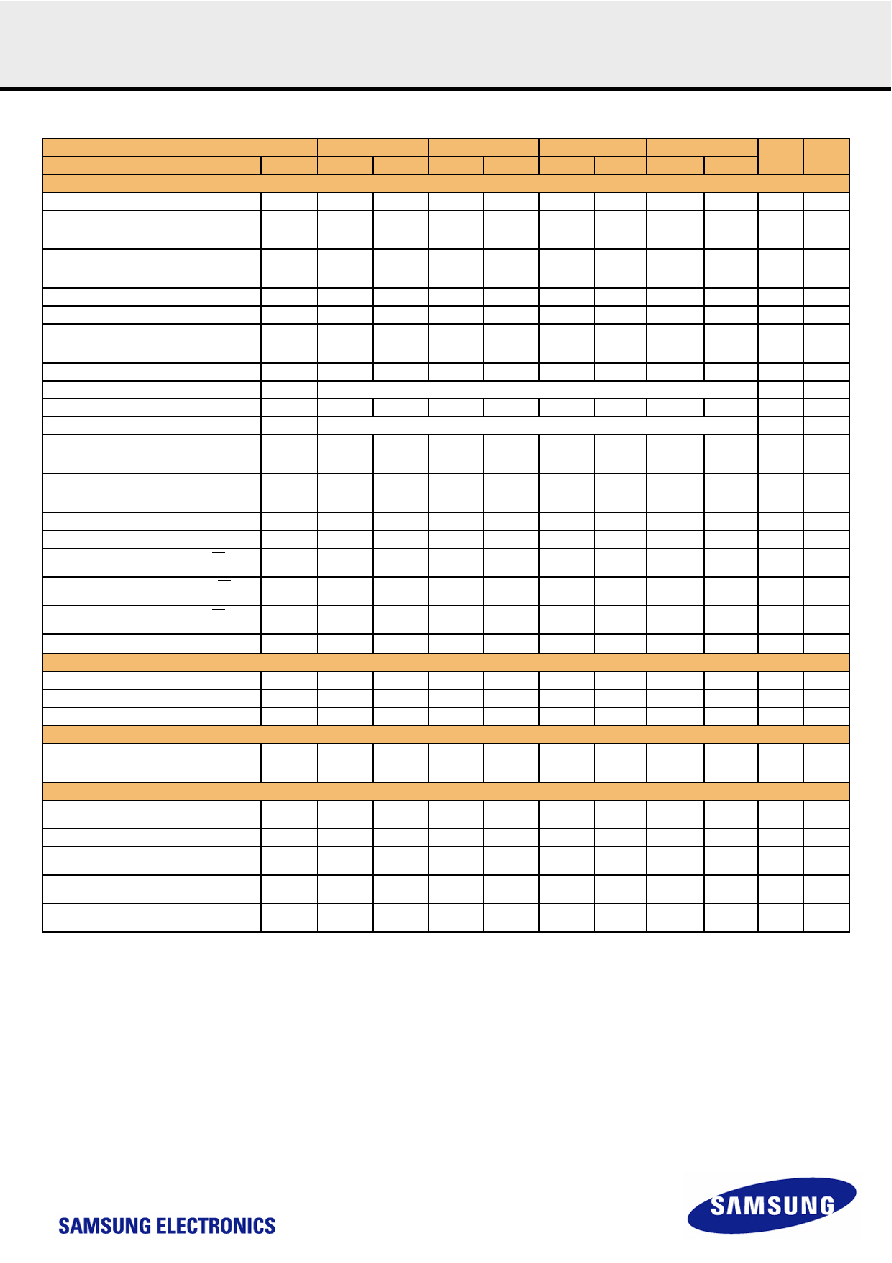

[ Table 18 ] Timing Parameters by Speed Bin (Cont.)

Speed

DDR3-800

DDR3-1066

DDR3-1333

DDR3-1600

Units

NOTE

Parameter

Symbol

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

Command and Address Timing

DLL locking time

tDLLK

512

-

512

-

512

-

512

-

nCK

internal READ Command to PRECHARGE Command

delay

tRTP

max

(4nCK,7.5ns

)

-

max

(4nCK,7.5ns

)

-

max

(4nCK,7.5ns

)

-

max

(4nCK,7.5ns)

-

e

Delay from start of internal write transaction to internal

read command

tWTR

max

(4nCK,7.5ns

)

-

max

(4nCK,7.5ns

)

-

max

(4nCK,7.5ns

)

-

max

(4nCK,7.5ns)

-

e,18

WRITE recovery time

tWR

15

-

15

-

15

-

15

-

ns

e,18

Mode Register Set command cycle time

tMRD

4

-

4

-

4

-

4

-

nCK

Mode Register Set command update delay

tMOD

max

(12nCK,15n

s)

-

max

(12nCK,15n

s)

-

max

(12nCK,15n

s)

-

max

(12nCK,15ns

)

-

CAS# to CAS# command delay

tCCD

4

-

4

-

4

-

4

-

nCK

Auto precharge write recovery + precharge time

tDAL(min)

WR + roundup (tRP / tCK(AVG))

nCK

Multi-Purpose Register Recovery Time

tMPRR

1

-

1

-

1

-

1

-

nCK

22

ACTIVE to PRECHARGE command period

tRAS

See “Speed Bins and CL, tRCD, tRP, tRC and tRAS for corresponding Bin” on page 40

ns

e

ACTIVE to ACTIVE command period for 1KB page

size

tRRD

max

(4nCK,10ns)

-

max

(4nCK,7.5ns

)

-

max

(4nCK,6ns)

-

max

(4nCK,6ns)

-

e

ACTIVE to ACTIVE command period for 2KB page

size

tRRD

max

(4nCK,10ns)

-

max

(4nCK,10ns)

-

max

(4nCK,7.5ns

)

-

max

(4nCK,7.5ns)

-

e

Four activate window for 1KB page size

tFAW

40

-

37.5

-

30

-

30

-

ns

e

Four activate window for 2KB page size

tFAW

50

-

50

-

45

-

40

-

ns

e

Command and Address setup time to CK, CK refer-

enced to VIH(AC) / VIL(AC) levels

tIS(base)

200

-

125

-

65

-

45

-

ps

b,16

Command and Address hold time from CK, CK refer-

enced to VIH(AC) / VIL(AC) levels

tIH(base)

275

-

200

-

140

-

120

-

ps

b,16

Command and Address setup time to CK, CK refer-

enced to VIH(AC) / VIL(AC) levels

tIS(base)

AC150

200 + 150

-

125 + 150

-

65+125

-

45+125

-

ps

b,16,27

Control & Address Input pulse width for each input

tIPW

900

-

780

-

620

-

560

-

ps

28

Calibration Timing

Power-up and RESET calibration time

tZQinitI

512

-

512

-

512

-

512

-

nCK

Normal operation Full calibration time

tZQoper

256

-

256

-

256

-

256

-

nCK

Normal operation short calibration time

tZQCS

64

-

64

-

64

-

64

-

nCK

23

Reset Timing

Exit Reset from CKE HIGH to a valid command

tXPR

max(5nCK,

tRFC +

10ns)

-

max(5nCK,

tRFC +

10ns)

-

max(5nCK,

tRFC +

10ns)

-

max(5nCK,

tRFC + 10ns)

-

Self Refresh Timing

Exit Self Refresh to commands not requiring a locked

DLL

tXS

max(5nCK,t

RFC + 10ns)

-

max(5nCK,t

RFC + 10ns)

-

max(5nCK,t

RFC + 10ns)

-

max(5nCK,tR

FC + 10ns)

-

Exit Self Refresh to commands requiring a locked DLL

tXSDLL

tDLLK(min)

-

tDLLK(min)

-

tDLLK(min)

-

tDLLK(min)

-

nCK

Minimum CKE low width for Self refresh entry to exit

timing

tCKESR

tCKE(min) +

1tCK

-

tCKE(min) +

1tCK

-

tCKE(min) +

1tCK

-

tCKE(min) +

1tCK

-

Valid Clock Requirement after Self Refresh Entry

(SRE) or Power-Down Entry (PDE)

tCKSRE

max(5nCK,

10ns)

-

max(5nCK,

10ns)

-

max(5nCK,

10ns)

-

max(5nCK,

10ns)

-

Valid Clock Requirement before Self Refresh Exit

(SRX) or Power-Down Exit (PDX) or Reset Exit

tCKSRX

max(5nCK,

10ns)

-

max(5nCK,

10ns)

-

max(5nCK,

10ns)

-

max(5nCK,

10ns)

-

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M393B5773CH0-CK0 | 256M X 72 MULTI DEVICE DRAM MODULE, 0.225 ns, DMA240 |

| M3950/1529A012 | TOGGLE SWITCH, 3PDT, LATCHED, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M83731/2327D110 | TOGGLE SWITCH, 3PDT, MOMENTARY, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M3950/1726A110 | TOGGLE SWITCH, 3PDT, LATCHED, 4A, 28VDC, THROUGH HOLE-STRAIGHT |

| M3E-R21ZQXFREQ | CRYSTAL OSCILLATOR, CLOCK, 1.5 MHz - 155.52 MHz, PECL OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M393B5273CH0-CK004 | 制造商:Samsung 功能描述:4GBYTE REGISTERED DIMM, DDR3-1600 - Trays |

| M393B5273DH-CH9E8 | 制造商:Samsung Semiconductor 功能描述:4GB 2RX8 PC3-8500R-07-00-B0-D1 - Trays |

| M393B5670EH1 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR3 SDRAM Memory |

| M393B5670EH1-CF801 | 制造商:Samsung Semiconductor 功能描述:2GB DDR3 REGISTERED DIMM, 1066MHZ, - Trays |

| M393B5670EH1-CH904 | 制造商:Samsung Semiconductor 功能描述:2GBYTE REGISTERED DIMM,DDR3-1333 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。