- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370849 > M37736MHB (Mitsubishi Electric Corporation) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M37736MHB |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單片16位CMOS微機 |

| 文件頁數(shù): | 93/96頁 |

| 文件大?。?/td> | 1328K |

| 代理商: | M37736MHB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當前第93頁第94頁第95頁第96頁

Rev.

No.

Rev.

date

1.00

First Edition

970507

2.00

The following are revised:

980731

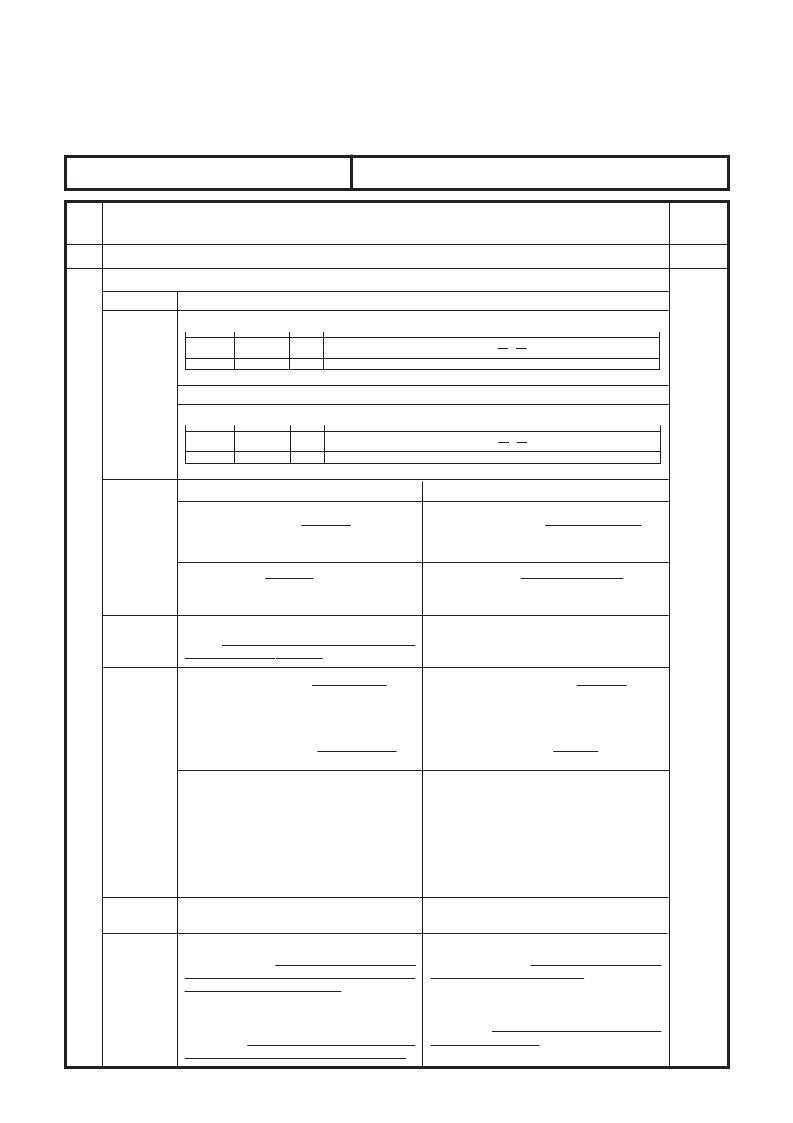

REVISION DESCRIPTION LIST

M37736MHBXXXGP Datasheet

(1)

Revision Description

Page

P4

P10

0

– P10

7

P5

Right column

Line 7

P5

Fig. 1

P9

Right column

Line 12

P66

Left column

Line 2

P66

Fig.71

P67

Fig. 73

P68

Right column

Line 2

Previous Version

Additionally, the internal ROM area can be modi-

fied by software.

Notes 1.

Internal ROM area can be modified. (Re-

fer to the section on ROM area modifica-

tion function.)

The CPU operates on an internal clock

φ

’s fre-

quency which is obtained by dividing the external

clock frequency f(X

IN

) by two.

The internal ROM size and its address area of the

M37736MHBXXXGP can be modified by the

memory allocation control register’s bits 0,1 and 2

shown in Figure 71.

Figure 73 shows the memory allocation in which

the internal ROM size and its address area are

modified.

Memory allocation selection bits

ROM size (ROM area)

0 0 0 : 124 Kbytes (addresses 001000

16

– 01FFFF

16

)

0 0 1 : 120 Kbytes (addresses 002000

16

– 01FFFF

16

)

1 1 0 : 96 Kbytes (addresses 008000

16

– 01FFFF

16

)

1 1 1 : 32 Kbytes (addresses 008000

16

– 00FFFF

16

)

Refer to page (2).

The M37736MHBXXXGP has 28 powerful

addressing modes. Refer to the SINGLE-CHIP 16-

BIT MICROCOMPUTERS DATA BOOK for the

details of each addressing mode.

MACHINE INSTRUCTION LIST

The M37736MHBXXXGP has 103 machine

instructions. Refer to the SINGLE-CHIP 16-BIT

MICROCOMPUTERS DATA BOOK for details.

Revised Version

Additionally, the internal ROM and RAM area can

be modified by software.

Notes 1.

Internal ROM and RAM area can be

modified. (Refer to the section on ROM

area modification function.)

The CPU operates on an internal clock

φ

’s

frequency.

The internal ROM size and RAM size of the

M37736MHBXXXGP can be modified by the

memory allocation control register’s bits 0,1 and 2

shown in Figure 71.

Figure 73 shows the memory allocation in which

the internal ROM size and RAM size are modified.

Memory allocation selection bits

ROM size RAM size

0 0 0 : 124 Kbytes 3968 bytes

0 0 1 : 120 Kbytes 3968 bytes

0 1 0 : 60 Kbytes 2048 bytes

1 0 0 : 32 Kbytes 2048 bytes

1 0 1 : 16 Kbytes 2048 bytes

1 1 0 : 96 Kbytes 3968 bytes

Refer to page (3).

The M37736MHBXXXGP has 28 powerful

addressing modes. Refer to the “7700 Family

Software Manual” for the details.

MACHINE INSTRUCTION LIST

The M37736MHBXXXGP has 103 machine

instructions. Refer to the “7700 Family Software

Manual” for the details.

Previous Version

P10

0

– P10

7

EVL0, EVL1

Output port P10

–

I/O

In addition to having the same functions as port P0 in the single-chip mode, P10

4

– P10

7

also

function as input pins for key input interrupt input (KI

0

– KI

3

).

These pins should be left open.

Output

Revised Version

P10

0

– P10

7

I/O port P10

I/O

In addition to having the same functions as port P0 in the single-chip mode, P10

4

– P10

7

also

function as input pins for key input interrupt input (KI

0

– KI

3

).

These pins should be left open.

EVL0, EVL1

–

Output

相關PDF資料 |

PDF描述 |

|---|---|

| M37736EHB | PROM VERSION OF M37736EHBXXXGP |

| M37736EHL | PROM VERSION OF M37736MHLXXXHP(MICROCOMPUTERS) |

| M37736EHBGS | PROM VERSION OF M37736EHBXXXGP |

| M37736EHLXXXHP | PROM VERSION OF M37736MHLXXXHP(MICROCOMPUTERS) |

| M37736MHLXXXHP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M37736MHBXXXGP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37736MHL | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37736MHLXXXHP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37753FFCFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE CHIP 16 BIT CMOS MICROCOMPUTER FLASH MEMORY VERSION |

| M37753FFCHP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE CHIP 16 BIT CMOS MICROCOMPUTER FLASH MEMORY VERSION |

發(fā)布緊急采購,3分鐘左右您將得到回復。