- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45027 > M34282M1-XXXGP 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | M34282M1-XXXGP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| 封裝: | 0.225 INCH, 0.65 MM PITCH, PLASTIC, SSOP-20 |

| 文件頁(yè)數(shù): | 67/70頁(yè) |

| 文件大小: | 625K |

| 代理商: | M34282M1-XXXGP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)當(dāng)前第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)

MITSUBISHI

ELECTRIC

7

MITSUBISHI MICROCOMPUTERS

4282 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

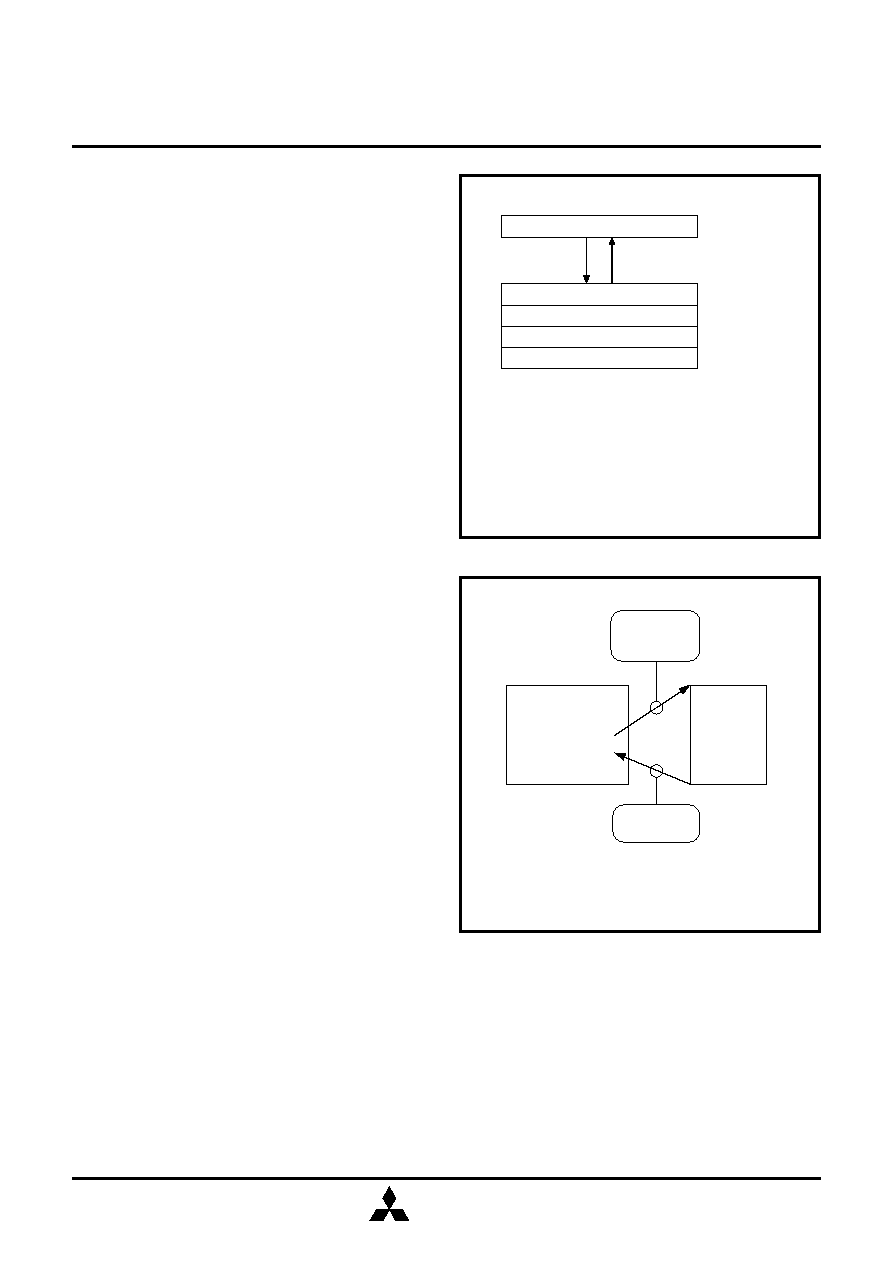

Fig. 5 Stack registers (SKs) structure

Fig. 6 Example of operation at subroutine call

(5) Most significant ROM code reference enable flag (URS)

URS flag controls whether to refer to the contents of the most

significant 1 bit (bit 8) of ROM code when executing the TABP

p instruction. If URS flag is “0,” the contents of the most

significant 1 bit of ROM code is not referred even when

executing the TABP p instruction. However, if URS flag is “1,”

the contents of the most significant 1 bit of ROM code is set to

flag CY when executing the TABP p instruction (Figure 4).

URS flag is “0” after system is released from reset and returned

from RAM back-up mode. It can be set to “1” with the URSC

instruction, but cannot be cleared to “0.”

(6) Stack registers (SKs) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the contents

of program counter (PC) just before branching until returning

to the original routine when;

performing a subroutine call, or

executing the table reference instruction (TABP p).

Stack registers (SKs) are four identical registers, so that

subroutines can be nested up to 4 levels. However, one of

stack registers is used when executing a table reference

instruction. Accordingly, be careful not to over the stack. The

contents of registers SKs are destroyed when 4 levels are

exceeded.

The register SK nesting level is pointed automatically by 2-bit

stack pointer (SP).

Figure 5 shows the stack registers (SKs) structure.

Figure 6 shows the example of operation at subroutine call.

(7) Skip flag

Skip flag controls skip decision for the conditional skip

instructions and continuous described skip instructions.

Note : The 4282 Group just invalidates the next instruction

when a skip is performed. The contents of program

counter is not increased by 2. Accordingly, the number

of cycles does not change even if skip is not performed.

However, the cycle count becomes “1” if the TABP p,

RT, or RTS instruction is skipped.

SK0

SK1

SK2

SK3

(SP) = 0

(SP) = 1

(SP) = 2

(SP) = 3

Program counter (PC)

Executing RT

instruction

Executing BM

instruction

Stack pointer (SP) points “3” at reset or

returning from RAM back-up mode. It points “0”

by executing the first BM instruction, and the

contents of program counter is stored in SK0.

When the BM instruction is executed after four

stack registers are used ((SP) = 3), (SP) = 0

and the contents of SK0 is destroyed.

Returning to the BM instruction execution

address with the RT instruction, and the BM

instruction is equivalent to the NOP instruction.

(SP)

← 0

(SK0)

← 000116

(PC)

← SUB1

Main program

000216 NOP

Address

000016 NOP

000116 BM SUB1

Subroutine

SUB1 :

NOP

RT

(PC)

← (SK0)

(SP)

← 3

Note:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M34286G2-XXXGP | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| M34286G2GP | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| M34502M4-XXXFP | 4-BIT, MROM, 4.4 MHz, MICROCONTROLLER, PDSO24 |

| M34502M2-XXXFP | 4-BIT, MROM, 4.4 MHz, MICROCONTROLLER, PDSO24 |

| M34506M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M34282M2 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34282M2-064GP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34282M2-XXXGP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34282T5-OPT | 制造商:Renesas Electronics Corporation 功能描述:DEV OPTION BOARD FOR 4282 GROUP/PC4400 - Boxed Product (Development Kits) |

| M34283 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。