- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄43903 > LC72134M PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 PDF資料下載

參數(shù)資料

| 型號(hào): | LC72134M |

| 元件分類(lèi): | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 |

| 封裝: | MFP-24 |

| 文件頁(yè)數(shù): | 17/27頁(yè) |

| 文件大小: | 463K |

| 代理商: | LC72134M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

No. 5814-24/27

LC72134M

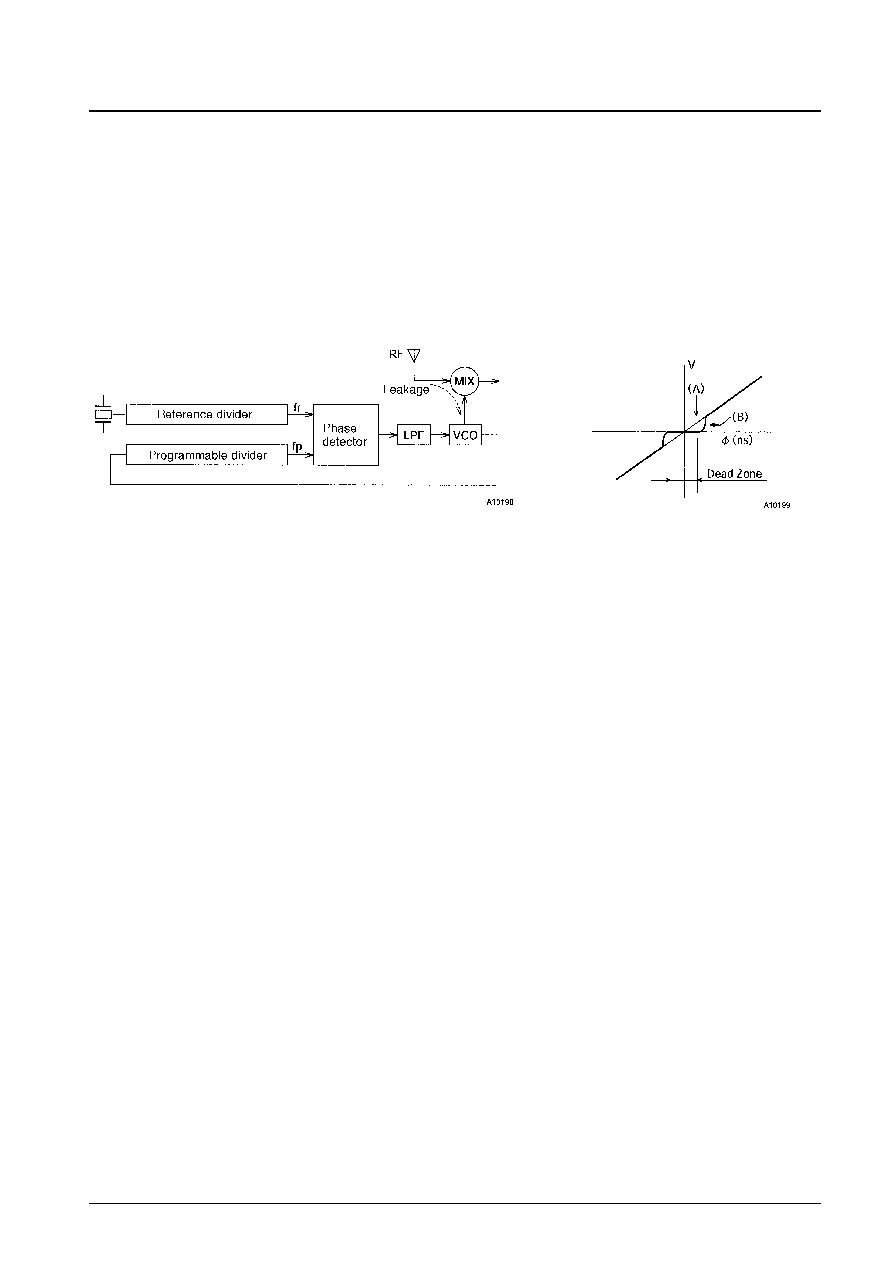

Dead Zone

As shown in figure 1, the phase comparator compares a reference frequency (fr) with fp. As shown in figure 2, the phase

comparator’s characteristics consist of an output voltage (V) that is proportional to the phase difference . However, due

to internal circuit delay and other factors, an actual circuit has a region (the dead zone, B) where the circuit cannot

actually compare the phases. To implement a receiver with a high S/N ratio, it is desirable that this region be as small as

possible. However, it is often desirable to have the dead zone be slightly wider in popularly-priced models. This is

because in certain cases, such as when there is a strong RF input, popularly-priced models can suffer from mixer to VCO

RF leakage that modulates the VCO. When the dead zone is small, the circuit outputs signals to correct this modulation

and this output further modulates the VCO. This further modulation may then generate beats with the RF signal.

Notes on the FMIN, AMIN, and IFIN pins

Coupling capacitors should be placed as close to their pin as possible. A capacitance of about 100 pF is desirable for

these capacitors. In particular, if the IFIN pin coupling capacitor is not held to under 100 pF, the time to reach the bias

level may become too long and incorrect counts may result due to the relationship with the wait time.

Notes on IF counting

→ Use the SD signal in conjunction with IF counting

When counting the IF frequency, the microcontroller must determine the presence or absence of the IF IC SD (station

detect) signal and turn on the IF counter buffer output and execute the IF count only if there is an SD signal. Auto-

search techniques that only use the IF counter are subject to incorrect stopping at points where there is no station due to

IF buffer leakage.

DO pin usage

The DO pin can be used for IF counter count completion checking and as an unlock detection output in addition to its

use in data output mode. It is also possible to have the DO pin reflect the state of an input pin to input that state to the

microcontroller.

Power supply pins

A capacitor of at least 2000 pF must be inserted between the power supply VDD and VSS pins for noise exclusion. This

capacitor must be placed as close as possible to the VDD and VSS pins.

Figure 1

Figure 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72135M | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LC72136NM | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO24 |

| LC72140M | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 |

| LC72140 | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDIP24 |

| LC72146 | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDIP24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72135M | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

| LC72135MA-AE | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| LC72135MA-Q-AE | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Tape and Reel 制造商:ON Semiconductor 功能描述:REEL / PLL FREQUENCY SYNTHESIZER |

| LC72135M-Q-TLM-E | 制造商:SANYO Semiconductor Co Ltd 功能描述: |

| LC72136 | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。