- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358757 > LC66354B (Sanyo Electric Co.,Ltd.) Quadruple 2-Input Positive-AND Gates 14-SO -40 to 85 PDF資料下載

參數(shù)資料

| 型號: | LC66354B |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | Quadruple 2-Input Positive-AND Gates 14-SO -40 to 85 |

| 中文描述: | 四位單片機與16 KB的片上微控制器檢察官辦公室胎膜早破 |

| 文件頁數(shù): | 25/27頁 |

| 文件大小: | 176K |

| 代理商: | LC66354B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁

Continued from preceding page.

No. 5487-25/27

LC66P2316

Continued on next page.

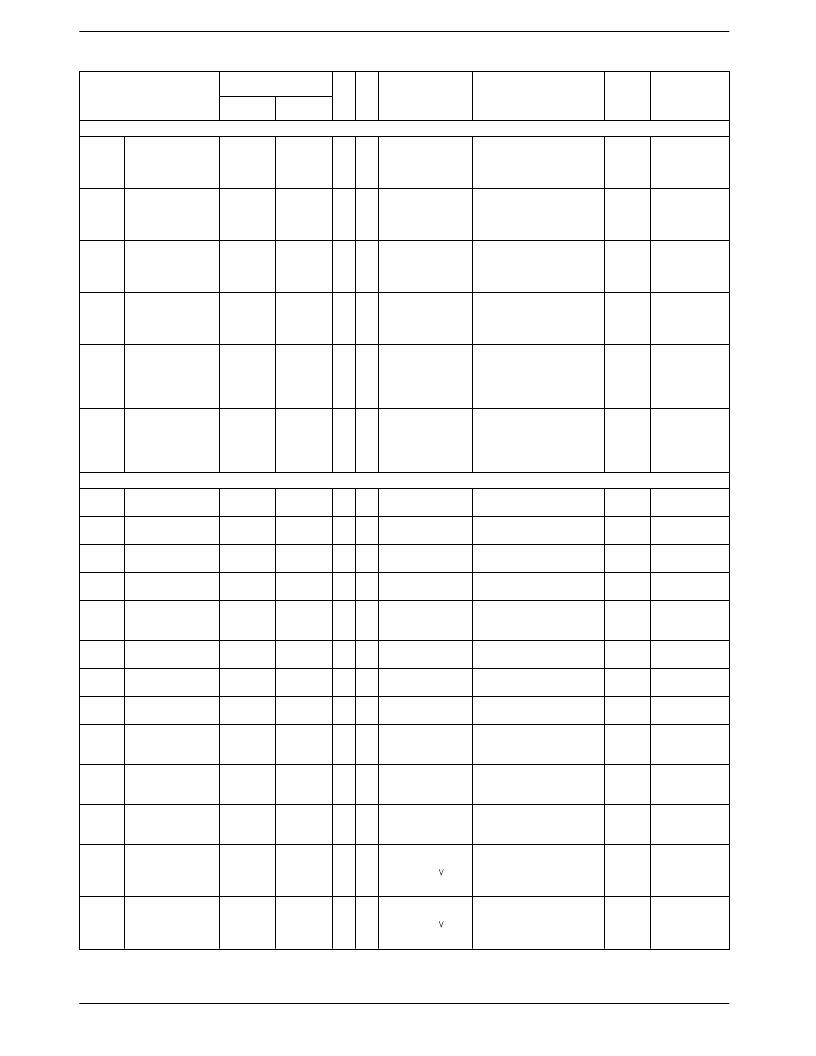

Instruction code

Affected

status

bits

Mnemonic

Operation

Description

Note

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

[Branch instructions]

PC7 to 0

←

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

if (CF) = 1

PC7 to 0

←

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

if (CF) = 0

PC7 to 0

←

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

if (ZF) = 1

PC7 to 0

←

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

if (ZF) = 0

Branch to the location in the

same page specified by P

7

to

P

0

if CF is one.

BC addr

Branch on CF

1 1 0 1

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

1 1 0 0

2

2

Branch to the location in the

same page specified by P

7

to

P

0

if CF is zero.

BNC

addr

Branch on no CF

1 0 0 1

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

1 1 0 0

2

2

Branch to the location in the

same page specified by P

7

to

P

0

if ZF is one.

BZ addr

Branch on ZF

1 1 0 1

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

1 1 0 1

2

2

Branch to the location in the

same page specified by P

7

to

P

0

if ZF is zero.

BNZ

addr

Branch on no ZF

1 0 0 1

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

1 1 0 1

2

2

PC7 to 0

←

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

if (Fn) = 1

Branch to the location in the

same page specified by P

0

to

P

7

if the flag (of the 16 user

flags) specified by n

3

n

2

n

1

n

0

is one.

BFn4

addr

1 1 1 1

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

n

3

n

2

n

1

n

0

Branch on flag bit

2

2

PC7 to 0

←

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

if (Fn) = 0

Branch to the location in the

same page specified by P

0

to

P

7

if the flag (of the 16 user

flags) specified by n

3

n

2

n

1

n

0

is zero.

BNFn4

addr

1 0 1 1

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

n

3

n

2

n

1

n

0

Branch on no flag bit

2

2

[I/O instructions]

IP0

Input port 0 to AC

0 0 1 0

0 0 0 0

1

1

AC

←

(P0)

Input the contents of port

0 to AC.

ZF

IP

Input port to AC

0 0 1 0

0 1 1 0

1

1

AC

←

[P (DP

L

)]

Input the contents of port

P (DP

L

) to AC.

Input the contents of port

P (DP

L

) to M (HL).

Input the contents of

P (i4) to AC.

ZF

IPM

Input port to M

0 0 0 1

1 0 0 1

1

1

M (HL)

←

[P (DP

L

)]

IPDR i4

Input port to

AC direct

1 1 0 0

0 1 1 0

1 1 1 1

I

3

I

2

I

1

I

0

2

2

AC

←

[P (i4)]

ZF

Input port 4, 5 to

E, AC respectively

1 1 0 0

1 1 0 1

1 1 1 1

0 1 0 0

E

←

[P (4)]

AC

←

[P (5)]

Input the contents of ports

P (4) and P (5) to E and AC

respectively.

IP45

2

2

OP

Output AC to port

0 0 1 0

0 1 0 1

1

1

P (DP

L

)

←

(AC)

Output the contents of AC to

port P (DP

L

).

Output the contents of M (HL)

to port P (DP

L

).

Output the contents of AC

to P (i4).

OPM

Output M to port

0 0 0 1

1 0 1 0

1

1

P (DP

L

)

←

[M (HL)]

OPDR i4

Output AC to

port direct

1 1 0 0

0 1 1 1

1 1 1 1

I

3

I

2

I

1

I

0

2

2

P (i4)

←

(AC)

Output E, AC to port

4, 5 respectively

1 1 0 0

1 1 0 1

1 1 1 1

0 1 0 1

P (4)

←

(E)

P (5)

←

(AC)

Output the contents of E and

AC to ports P (4) and P (5)

respectively.

OP45

2

2

Set to one the bit in port

P (DP

L

) specified by the

immediate data t

1

t

0

.

Clear to zero the bit in port

P (DP

L

) specified by the

immediate data t

1

t

0

.

Take the logical AND of P (P

3

to P

0

) and the immediate data

I

3

I

2

I

1

I

0

and output the result

to P (P

3

to P

0

).

Take the logical OR of P (P

3

to P

0

) and the immediate data ZF

I

3

I

2

I

1

I

0

and output the result

to P (P

3

to P

0

).

SPB t2

Set port bit

0 0 0 0

1 0 t

1

t

0

1

1

[P (DP

L

), t2]

←

1

RPB t2

Reset port bit

0 0 1 0

1 0 t

1

t

0

1

1

[P (DP

L

), t2]

←

0

ZF

And port with

immediate data then

output

P (P

3

to P

0

)

←

[P (P

3

to P

0

)]

I

3

to I

0

ANDPDR

i4, p4

1 1 0 0

I

3

I

2

I

1

I

0

0 1 0 1

P

3

P

2

P

1

P

0

2

2

ZF

Or port with

immediate data then

output

P (P

3

to P

0

)

←

[P (P

3

to P

0

)]

I

3

to I

0

ORPDR

i4, p4

1 1 0 0

I

3

I

2

I

1

I

0

0 1 0 0

P

3

P

2

P

1

P

0

2

2

N

b

N

c

相關PDF資料 |

PDF描述 |

|---|---|

| LC66354C | Quadruple 2-Input Positive-AND Gates 14-TSSOP -40 to 85 |

| LC66356C | Quadruple Bus Buffer Gates With 3-State Outputs 14-VQFN -40 to 85 |

| LC66358B | Four-bit Single-Chip Microcontrollers On-Chip 8 K-byte ROM(4位單片微控制器(帶8K字節(jié)片上ROM)) |

| LC66358S | Four-Bit Single-Chip Microcontrollers with 6k and 8k of On-Chip ROM |

| LC66358V | 3-Line to 8-Line Decoder / Demultiplexer 16-TVSOP -40 to 85 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LC66354C | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Four-Bit Single-Chip Microcontroller with 16 KB of On-Chip OTP PROM |

| LC66354S | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Four-Bit Single-Chip Microcontroller with 16 KB of On-Chip EPROM |

| LC66354V | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:4-bit Microcontroller with Built-in PROM |

| LC66356A | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Four-Bit Single-Chip Microcontroller with 16 KB of On-Chip OTP PROM |

| LC66356B | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Four-Bit Single-Chip Microcontroller with 16 KB of On-Chip OTP PROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。