- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358755 > LC374500ST (Sanyo Electric Co.,Ltd.) Internal Synchronization Silicon Gate 4M (524288-word x 8-bit) mask ROM Pin Compatible with Flash Memory PDF資料下載

參數(shù)資料

| 型號: | LC374500ST |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | Internal Synchronization Silicon Gate 4M (524288-word x 8-bit) mask ROM Pin Compatible with Flash Memory |

| 中文描述: | 內(nèi)同步硅門4米(524288字× 8位)與掩膜ROM閃存引腳兼容 |

| 文件頁數(shù): | 4/4頁 |

| 文件大小: | 46K |

| 代理商: | LC374500ST |

PS No. 5610-4/4

LC374500ST

This catalog provides information as of April, 1998. Specifications and information herein are subject to change

without notice.

I

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace

equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of

which may directly or indirectly cause injury, death or property loss.

I

Anyone purchasing any products described or contained herein for an above-mentioned use shall:

Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and

distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all

damages, cost and expenses associated with such use:

Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on

SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees

jointly or severally.

I

Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for

volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied

regarding its use or any infringements of intellectual property rights or other rights of third parties.

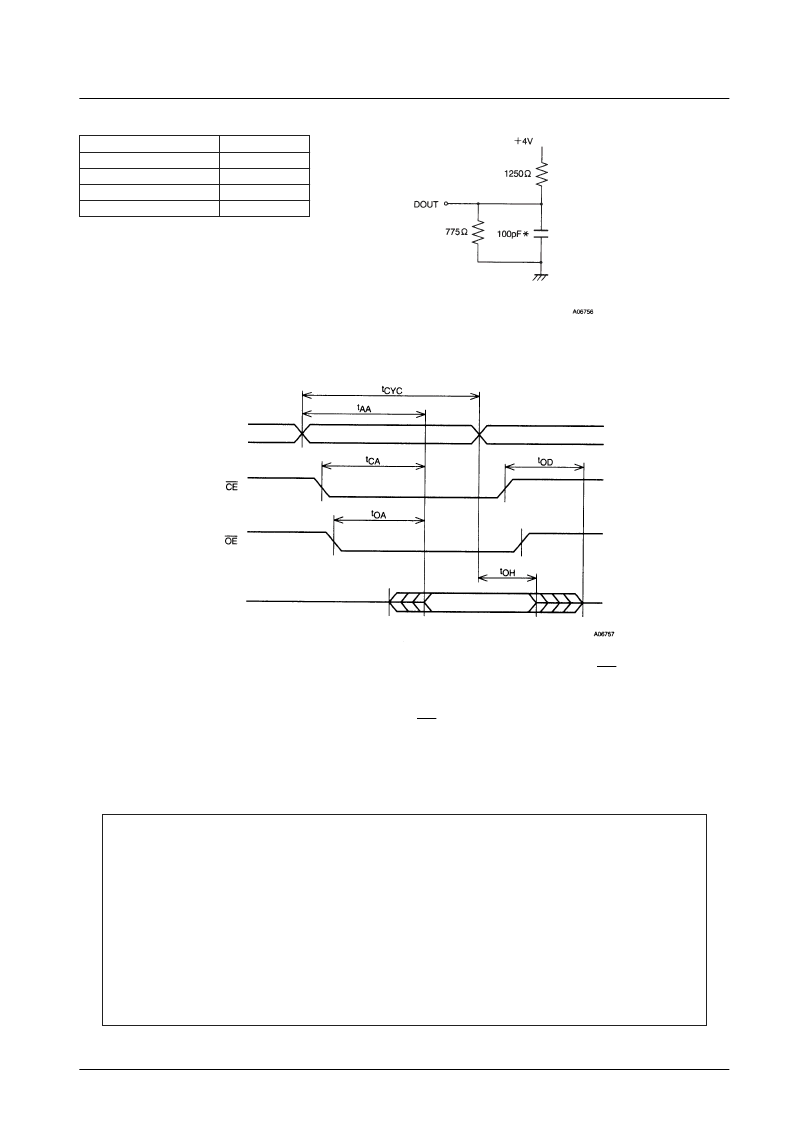

Test Conditions

Input voltage amplitude

0.4 V to 2.8 V

Rise/fall time

5 ns

Input discrimination level

1.5 V

Output discrimination level

1.5 V

Output capacitance

See figure 1

*

: Includes the oscilloscope and jig capacitances.

Address input

Valid Address

Valid data

Data output

High impedance

Figure 1 Output Load Circuit

Timing Waveforms

Notes on System Design

This LSI adopts the ATD technique, in which operation starts when a change in either the CE or address inputs is

detected. This means that the output data immediately after power is applied is invalid. When using this LSI as program

memory for Z80 and similar microprocessors, applications must take into account the fact that valid data will not be

output after power is first applied unless the value of either the CE or at least one of the address lines is changed after the

power supply has stabilized.

Another point due to the use of the ATD technique is that this LSI is sensitive to input noise. Do not apply voltages

outside the allowable DC input levels for extended periods and do not apply input voltages with large noise components.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC374TWN1-25P-A1 | 3-mm Round LED |

| LC374TWN1-25Q-A1 | 3-mm Round LED |

| LC374TWN1-35P-A1 | 3-mm Round LED |

| LC374TWN1-35Q-A1 | 3-mm Round LED |

| LC374TWN1-65P-A1 | 3-mm Round LED |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC374TWN1-25G-A1 | 制造商:MARKTECH 制造商全稱:Marktech Corporate 功能描述:Ultra Bright White 3mm LED |

| LC374TWN1-25H-A1 | 制造商:MARKTECH 制造商全稱:Marktech Corporate 功能描述:Ultra Bright White 3mm LED |

| LC374TWN1-25P-A1 | 制造商:CREE 制造商全稱:Cree, Inc 功能描述:3-mm Round LED |

| LC374TWN1-25Q-A1 | 制造商:CREE 制造商全稱:Cree, Inc 功能描述:3-mm Round LED |

| LC374TWN1-35P-A1 | 制造商:CREE 制造商全稱:Cree, Inc 功能描述:3-mm Round LED |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。