- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384544 > ISPLSI81080V-125LB492 (LATTICE SEMICONDUCTOR CORP) 3.3V In-System Programmable SuperBIG⑩ High Density PLD PDF資料下載

參數(shù)資料

| 型號: | ISPLSI81080V-125LB492 |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| 中文描述: | EE PLD, 14.5 ns, PBGA492 |

| 封裝: | BGA-492 |

| 文件頁數(shù): | 20/26頁 |

| 文件大?。?/td> | 333K |

| 代理商: | ISPLSI81080V-125LB492 |

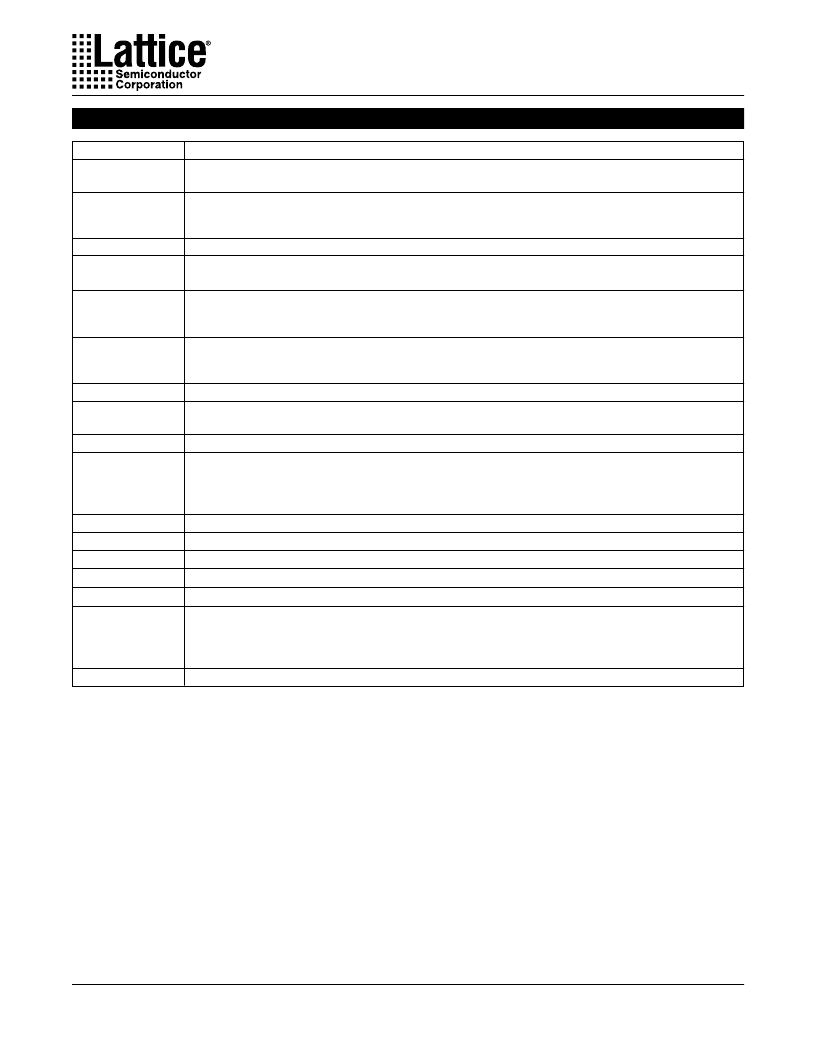

Specifications

ispLSI 81080V

20

CLK0, CLK1,

CLK2

CLKEN

Dedicated clock input for the GLB registers only. These clock inputs are connected to one of the clock

inputs of all GLB registers in the device.

Dedicated clock enable input for the GLB registers only. This input is available as a clock enable for

each GLB register in the device. Use of the clock enable input eliminates the need for the user to gate

the clock to the register.

Ground (GND)

Global Output Enable inputs.

GND

GOE0, GOE1,

GOE2, GOE3

SET/RESET

Dedicated reset/preset pin connected to ALL registers in the device, GLB registers and I/O registers.

Each register can independently choose to be reset or preset when this signal goes active. The active

polarity is user-selectable.

Dedicated clock enable input for the I/O registers only. This input is available as a clock enable input for

all I/O registers in the device. Use of the clock enable input eliminates the need for the user to tie the

clock to the I/O register.

Input/Output

–

These are the general purpose I/O used by the logic array.

Embedded Port Enable Pin

–

When this pin is high, the port is enabled. When this pin is low, the

state machine is held at reset asynchronously and TCK, TMS and TDI are ignored.

Input

–

This signal is the Test Mode Select input signal.

Dedicated clock inputs for the I/O registers only. These clock inputs are connected to the I/O registers

on the same side of the device only, they are not connected to all of the I/O registers. Use of these

quadrant I/O clocks gives the fastest tco from the device.

IOCLKEN

I/O

EPEN

TMS

QIOCLK0,

QIOCLK1,

QIOCLK2,

QIOCLK3

TCK

TDI

TDO

TOE

VCC

VCCIO

Input

–

This signal is the Test Clock input signal.

Input

–

This signal is the Test Data input signal.

Output

–

This signal is the Test Data Out Output Signal.

Test Output Enable. Tristates all I/O pins when a logic low is driven.

Vcc

Power supply for the output drivers. The internal logic of the device is connected to VCC which is

always 3.3V. The output drivers are connected to VCCIO which can be equal to VCC or 2.5V. This

allows the output drivers to be powered from 2.5V, for example, to interface directly with another 2.5V

device.

No connect.

1. NC pins are not to be connected to any active signals, VCC or GND.

NC

1

Signal Descriptions

Signal Name Description

相關PDF資料 |

PDF描述 |

|---|---|

| ISPLSI81080V-90LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-125LB272 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-125LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-60LB272 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

| ISPLSI8600V-60LB492 | 3.3V In-System Programmable SuperBIG⑩ High Density PLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ISPLSI81080V-60LB272 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ISPLSI81080V-60LB272I | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ISPLSI81080V-60LB492 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Lattice Semiconductor Corporation 功能描述: |

| ISPLSI81080V-90LB272 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ISPLSI81080V-90LB492 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。