- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384537 > ISPLSI1032E-80LT (Lattice Semiconductor Corporation) High-Density Programmable Logic PDF資料下載

參數(shù)資料

| 型號(hào): | ISPLSI1032E-80LT |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | High-Density Programmable Logic |

| 中文描述: | 高密度可編程邏輯 |

| 文件頁(yè)數(shù): | 8/16頁(yè) |

| 文件大小: | 164K |

| 代理商: | ISPLSI1032E-80LT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

8

Specifications

ispLSI 1032E

USEispLS 1032EAFORNEWDESGNS

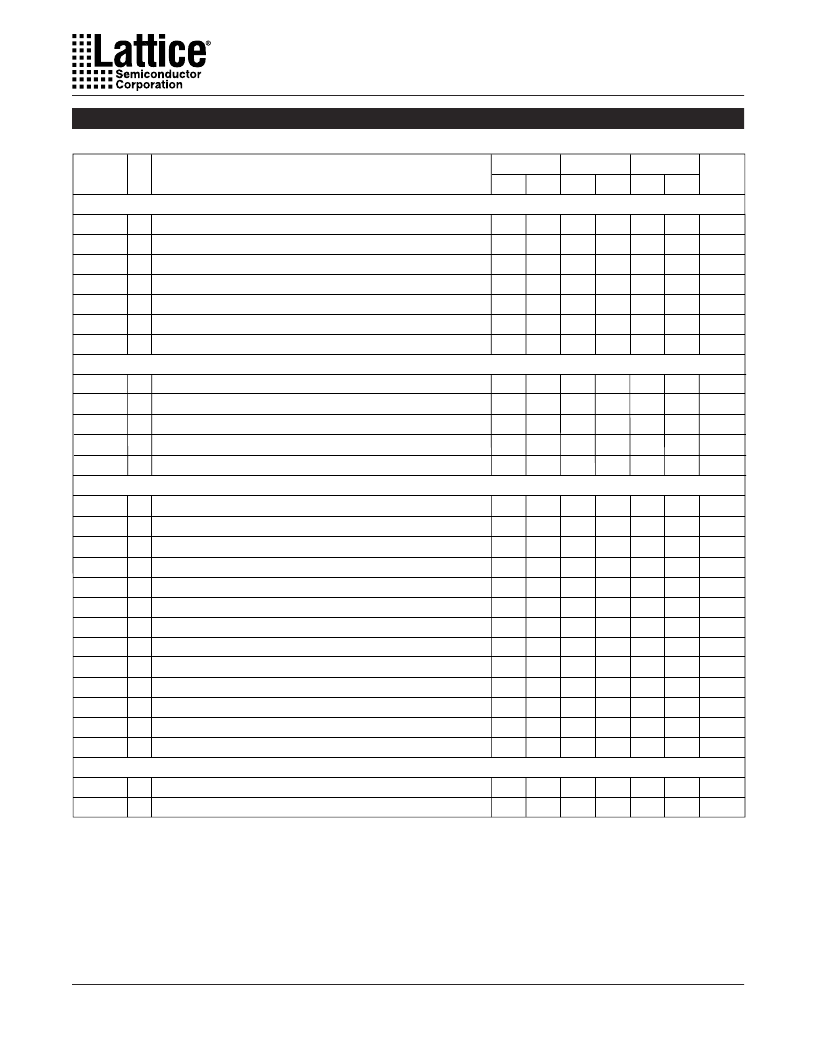

Internal Timing Parameters

1

GRP Delay, 32 GLB Loads

t

iobp

t

iolat

t

iosu

t

ioh

t

ioco

t

ior

t

din

1. Internal Timing Parameters are not tested and are for reference only.

2. Refer to Timing Model in this data sheet for further details.

3. The XOR adjacent path can only be used by hard macros.

Table 2-0036B/1032E

Inputs

UNITS

-80

MIN.

-70

MIN.

MAX.

MAX.

DESCRIPTION

#

2

PARAM.

22 I/O Register Bypass

23 I/O Latch Delay

24 I/O Register Setup Time before Clock

25 I/O Register Hold Time after Clock

26 I/O Register Clock to Out Delay

27 I/O Register Reset to Out Delay

28 Dedicated Input Delay

–

–

ns

ns

ns

ns

ns

ns

ns

t

grp32

GLB

t

4ptbpc

t

4ptbpr

33

–

ns

t

1ptxor

t

20ptxor 37 20 Prod. Term/XOR Path Delay

t

xoradj

38 XOR Adjacent Path Delay

t

gbp

39 GLB Register Bypass Delay

t

gsu

40 GLB Register Setup Time before Clock

t

gh

41 GLB Register Hold Time after Clock

t

gco

42 GLB Register Clock to Output Delay

t

gro

43 GLB Register Reset to Output Delay

t

ptre

44 GLB Prod.Term Reset to Register Delay

t

ptoe

45 GLB Prod. Term Output Enable to I/O Cell Delay

t

ptck

46 GLB Prod. Term Clock Delay

ORP

t

orp

47 ORP Delay

t

orpbp

48 ORP Bypass Delay

36 1 Prod.Term/XOR Path Delay

–

–

–

–

ns

ns

ns

ns

ns

ns

–

ns

–

–

–

ns

ns

ns

ns

GRP

t

grp1

MIN. MAX.

34 4 Prod.Term Bypass Path Delay (Combinatorial)

–

ns

35 4 Prod. Term Bypass Path Delay (Registered)

–

ns

0.5

7.9

4.5

–

–

ns

ns

0.0

3.5

0.0

–

–

–

t

grp16

32 GRP Delay, 16 GLB Loads

–

ns

t

grp8

31 GRP Delay, 8 GLB Loads

–

ns

t

grp4

30 GRP Delay, 4 GLB Loads

–

ns

29 GRP Delay, 1 GLB Load

–

ns

0.3

2.7

–

–

5.4

5.4

2.8

4.8

6.6

7.8

8.2

1.3

2.9

6.4

5.5

8.0

5.8

7.1

6.7

–

–

1.0

0.0

3.5

2.8

2.5

2.2

–

–

–

–

–

–

–

–

–

–

–

–

–

0.5

8.8

4.8

–

–

4.0

0.0

–

–

–

–

–

–

–

0.3

3.3

–

–

6.1

6.0

2.8

5.6

8.3

8.7

9.2

1.6

2.9

6.8

5.8

9.0

6.2

8.8

7.2

–

–

1.0

4.0

3.2

2.5

2.5

-90

–

–

–

–

–

–

–

–

–

–

–

–

–

–

0.2

6.8

4.1

–

3.5

0.0

–

–

–

–

–

–

–

0.3

2.3

–

–

5.0

5.0

2.6

4.4

5.6

6.8

7.1

0.4

2.9

6.3

5.1

7.1

5.3

5.7

6.1

–

–

1.0

0.0

3.2

2.6

2.3

2.1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPLSI1032E-90LJ | In-System Programmable High Density PLD |

| ISPLSI1032E-90LJ | High-Density Programmable Logic |

| ISPLSI1032E-90LT | In-System Programmable High Density PLD |

| ISPLSI1032E-90LT | High-Density Programmable Logic |

| ISPLSI1032E-100LT | In-System Programmable High Density PLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPLSI1032E80LTI | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable High Density PLD |

| ISPLSI1032E80LTN | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable High Density PLD |

| ISPLSI1032E80LTNI | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable High Density PLD |

| ISPLSI1032E90LJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| ISPLSI1032E-90LJ | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable High Density PLD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。