- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384484 > IP82C50A-5 (HARRIS SEMICONDUCTOR) CMOS Asynchronous Communications Element PDF資料下載

參數(shù)資料

| 型號(hào): | IP82C50A-5 |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CMOS Asynchronous Communications Element |

| 中文描述: | 1 CHANNEL(S), 625K bps, SERIAL COMM CONTROLLER, PDIP40 |

| 文件頁(yè)數(shù): | 12/21頁(yè) |

| 文件大?。?/td> | 101K |

| 代理商: | IP82C50A-5 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

12

Modem Status Registers. The contents of the Interrupt

Enable Register are indicated in Table 3 and are described

below.

IER(0):

When programmed high (IER(0) = Logic 1), IER(0)

enables Received Data Available interrupt.

IER(1):

When programmed high (IER(1) = Logic 1), IER(1)

enables the Transmitter Holding Register Empty interrupt.

IER(2):

When Programmed high (IER(2) = Logic 1), IER(2)

enables the Receiver Line Status interrupt.

IER(3):

When programmed high (IER(3) = Logic 1), IER(3)

enables the Modem Status interrupt.

IER(4) - IER(7):

These four bits of the IER are logic 0.

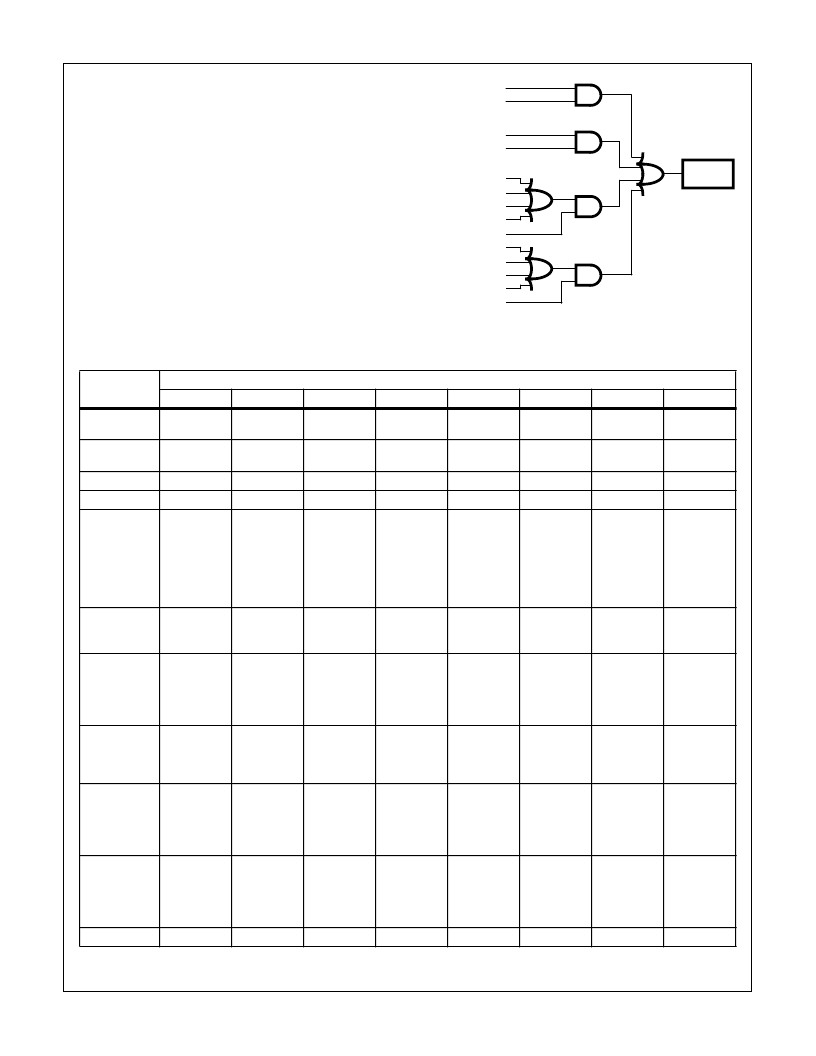

FIGURE 1. 82C50A INTERRUPT CONTROL STRUCTURE

INTRPT

PIN 30

DR (LSR BIT 0)

ERBFI (IER BIT 0)

OE (LSR BIT 1)

PE (LSR BIT 2)

FE (LSR BIT 3)

BI (LSR BIT 4)

ELSI (IER BIT 2)

DCTS (MSR BIT 0)

DDSR (MSR BIT 1)

TERI (MSR BIT 2)

DDCD (MSR BIT 3)

EDSSI (IER BIT 3)

THRE (LSR BIT 5)

ETBEI (IER BIT 1)

TABLE 3. 82C50A ACCESSIBLE REGISTER SUMMARY

(NOTE: See Table 1 for how to access these registers.)

REGISTER

MNEMONIC

REGISTER BIT NUMBER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

RBR

(Read Only)

Data Bit 7

(MSB)

Data Bit 6

Data Bit 5

Data Bit 4

Data Bit 3

Data Bit 2

Data Bit 1

Data Bit 0

(LSB)

THR

(Write Only)

Data Bit 7

Data Bit 6

Data Bit 5

Data Bit 4

Data Bit 3

Data Bit 2

Data Bit 1

Data Bit 0

DLL

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

DLM

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

IER

0

0

0

0

(EDSSI)

Enable

Modem

Status

Interrupt

(ELSI)

Enable

Receiver

Line

Status

Interrupt

(ETBEI)

Enable

Transmitter

Holding

Register

Empty

Interrupt

(ERBFI)

Enable

Received

Data

Available

Interrupt

IIR

(Read Only)

0

0

0

0

0

Interrupt ID

Bit (1)

Interrupt ID

Bit (0)

“0” 1F

Interrupt

Pending

LCR

(DLAB)

Divisor

Latch

Access

Bit

Set Break

Stick Parity

(EPS)

Even Parity

Select

(PEN)

Parity

Enable

(STB)

Number

of Stop

Bits

(WLSB1)

Word

Length

Select

Bit 1

(WLSB0)

Word

Length

Select

Bit 0

MCR

0

0

0

Loop

Out 2

Out 1

(RTS)

Request

to Send

(DTR)

Data

Terminal

Ready

LSR

0

(TEMT)

Transmitter

Empty

(THRE)

Transmitter

Holding

Register

Empty

(BI)

Break

Interrupt

(FE)

Framing

Error

(PE)

Parity

Error

(OE)

Overrun

Error

(DR)

Data

Ready

MSR

(DCD)

Data

Carrier

Detect

(RI)

Ring

Indicator

(DSR)

Data

Set

Ready

(CTS)

Clear

to

Send

(DDCD)

Delta

Data

Carrier

Detect

(TERI)

Trailing

Edge

Ring

Indicator

(DDSR)

Delta

Data

Set

Ready

(DCTS)

Delta

Clear

to

Send

SCR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

LSB, Data Bit 0 is the first bit transmitted or received.

82C50A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP82C52 | CMOS Serial Controller Interface |

| IP82C55AZ | CMOS Programmable Peripheral Interface |

| IP82C82 | CMOS Octal Latching Bus Driver |

| IPB05N03LA | OptiMOS 2 Power-Transistor |

| IPB05N03L | OptiMOS Buck converter series |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IP82C52 | 功能描述:UART 接口集成電路 PERIPH UART/BRG 5V 16MHZ IND RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| IP82C52/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UART |

| IP82C54 | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 PERIPH PRG-CNTR 5V 8MHZ 24PDIP IND RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

| IP82C54/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Timer Circuit |

| IP82C54-10 | 功能描述:計(jì)時(shí)器和支持產(chǎn)品 PERIPH PRG-CNTR 5V 10MHZ 24PDIP IND RoHS:否 制造商:Micrel 類型:Standard 封裝 / 箱體:SOT-23 內(nèi)部定時(shí)器數(shù)量:1 電源電壓-最大:18 V 電源電壓-最小:2.7 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。