- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384484 > IP80C86-2 (INTERSIL CORP) CMOS 16-Bit Microprocessor PDF資料下載

參數(shù)資料

| 型號: | IP80C86-2 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CMOS 16-Bit Microprocessor |

| 中文描述: | 16-BIT, 8 MHz, MICROPROCESSOR, PDIP40 |

| 封裝: | PLASTIC, DIP-40 |

| 文件頁數(shù): | 5/35頁 |

| 文件大小: | 339K |

| 代理商: | IP80C86-2 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

3-145

INTR

18

I

INTERRUPT REQUEST: is a level triggered input which is sampled during the last clock cycle

of each instruction to determine if the processor should enter into an interrupt acknowledge op-

eration. A subroutine is vectored to via an interrupt vector lookup table located in system mem-

ory. It can be internally masked by software resetting the interrupt enable bit.

lNTR is internally synchronized. This signal is active HIGH.

TEST

23

I

TEST: input is examined by the “Wait” instruction. If the TEST input is LOW execution continues,

otherwise the processor waits in an “Idle” state. This input is synchronized internally during each

clock cycle on the leading edge of CLK.

NMI

17

I

NON-MASKABLE INTERRUPT: is an edge triggered input which causes a type 2 interrupt. A

subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is

not maskable internally by software. A transition from LOW to HIGH initiates the interrupt at the

end of the current instruction. This input is internally synchronized.

RESET

21

I

RESET: causes the processor to immediately terminate its present activity. The signal must tran-

sition LOW to HIGH and remain active HIGH for at least four clock cycles. It restarts execution,

as described in the Instruction Set description, when RESET returns LOW. RESET is internally

synchronized.

CLK

19

I

CLOCK: provides the basic timing for the processor and bus controller. It is asymmetric with a

33% duty cycle to provide optimized internal timing.

VCC

40

VCC: +5V power supply pin. A 0.1

μ

F capacitor between pins 20 and 40 is recommended for de-

coupling.

GND

1, 20

GND: Ground. Note: both must be connected. A 0.1

μ

F capacitor between pins 1 and 20 is rec-

ommended for decoupling.

MN/MX

33

I

MINIMUM/MAXIMUM: Indicates what mode the processor is to operate in. The two modes are

discussed in the following sections.

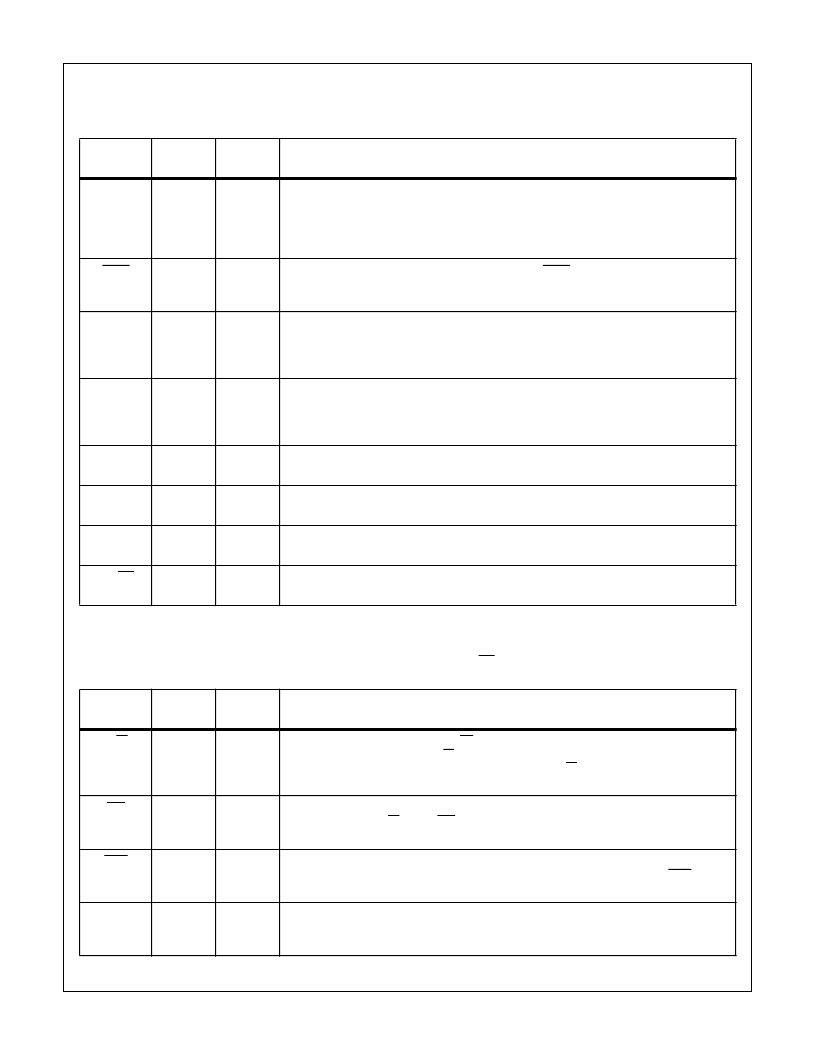

Minimum Mode System

The following pin function descriptions are for the 80C86 in minimum mode (i.e., MN/MX = V

CC

). Only the pin functions which are unique to

minimum mode are described; all other pin functions are as described below.

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

M/IO

28

O

STATUS LINE: logically equivalent to S2 in the maximum mode. It is used to distinguish a mem-

ory access from an I/O access. M/lO becomes valid in the T4 preceding a bus cycle and remains

valid until the final T4 of the cycle (M = HIGH, I/O = LOW). M/lO is held to a high impedance logic

one during local bus “hold acknowledge”.

WR

29

O

WRITE: indicates that the processor is performing a write memory or write I/O cycle, depending

on the state of the M/IO signal. WR is active for T2, T3 and TW of any write cycle. It is active

LOW, and is held to high impedance logic one during local bus “hold acknowledge”.

INTA

24

O

INTERRUPT ACKNOWLEDGE: is used as a read strobe for interrupt acknowledge cycles. It is

active LOW during T2, T3 and TW of each interrupt acknowledge cycle. Note that INTA is never

floated.

ALE

25

O

ADDRESS LATCH ENABLE: is provided by the processor to latch the address into the

82C82/82C83 address latch. It is a HIGH pulse active during clock LOW of T1 of any bus cycle.

Note that ALE is never floated.

Pin Description

(Continued)

The following pin function descriptions are for 80C86 systems in either minimum or maximum mode. The “Local Bus” in these description is

the direct multiplexed bus interface connection to the 80C86 (without regard to additional bus buffers).

SYMBOL

PIN

NUMBER

TYPE

DESCRIPTION

80C86

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP80C88 | CMOS 8/16-Bit Microprocessor |

| IP80C88-2 | CMOS 8/16-Bit Microprocessor |

| IP82C50A-5 | CMOS Asynchronous Communications Element |

| IP82C52 | CMOS Serial Controller Interface |

| IP82C55AZ | CMOS Programmable Peripheral Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IP80C88 | 功能描述:微處理器 - MPU CPU 8/16BIT 5V 5MHZ IND RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| IP80C88/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| IP80C88-2 | 功能描述:微處理器 - MPU CPU 8/16BIT 5V 8MHZ IND RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| IP80C88-2/+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16-Bit Microprocessor |

| IP80C88-2S2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。