- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383084 > ICL7112LCDL (INTERSIL CORP) 2.0 Gbps 4x4 Crosspoint Switch 38-TSSOP -40 to 85 PDF資料下載

參數(shù)資料

| 型號: | ICL7112LCDL |

| 廠商: | INTERSIL CORP |

| 元件分類: | ADC |

| 英文描述: | 2.0 Gbps 4x4 Crosspoint Switch 38-TSSOP -40 to 85 |

| 中文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP40 |

| 封裝: | CERDIP-40 |

| 文件頁數(shù): | 4/14頁 |

| 文件大小: | 758K |

| 代理商: | ICL7112LCDL |

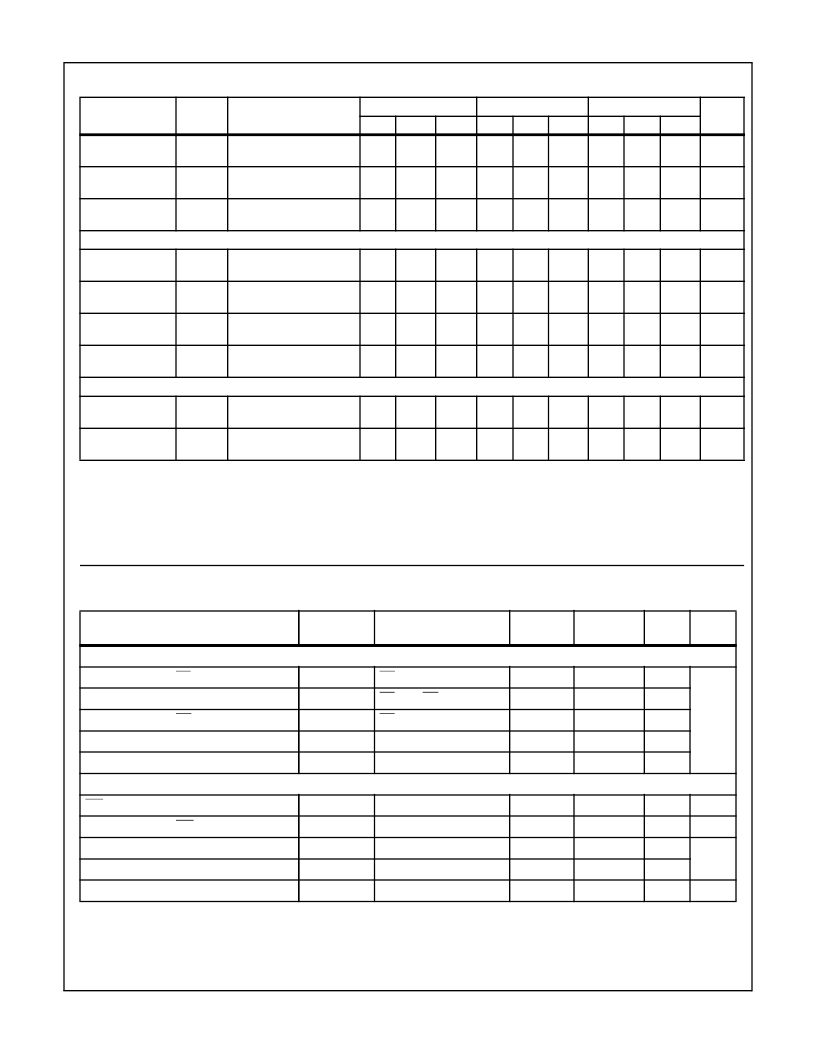

6-4

High State

Input Voltage

V

IH

T

MIN

-T

MAX

2.4

-

-

2.4

-

-

2.4

-

-

V

Logic Input

Current

I

LIH

0 < V

IN

< V

+

-

1

10

-

1

10

-

1

10

μ

A

Logic Input

Capacitance

C

IN

-

15

-

-

15

-

-

15

-

pF

LOGIC OUTPUT

Low State Output

Voltage

V

OL

I

OUT

= 1.6mA

T

MIN

-T

MAX

-

-

0.4

-

-

0.4

-

-

0.4

V

High State Output

Voltage

V

OH

I

OUT

= -200

μ

A

T

MIN

-T

MAX

2.8

-

-

2.8

-

-

2.8

-

-

V

Three-State Output

Current

I

OX

0 < V

OUT

< V

+

-

1

-

-

1

-

-

1

-

μ

A

Logic Output

Capacitance

C

OUT

Three-State

-

15

-

-

15

-

-

15

-

pF

POWER REQUIREMENTS

Supply Voltage

Range

V

SUPPLY

Functional Operation Only

±

4.5

-

±

6.0

±

4.5

-

±

6.0

±

4.5

-

±

6.0

V

Supply Current,

I+, I-

I

SUPPLY

R

M

T

MIN

-T

MAX

-

2

4

6

-

2

4

6

-

2

4

6

mA

NOTES:

4. Full scale range (FSR) is 10V (reference adjusted).

5. Assume all leads are soldered or welded to printed circuit board.

6. “J” and “K” versions not production tested. Guaranteed by Integral Linearity Test.

7. Typical values are not tested, for reference only.

8. Not production tested. Guaranteed by design.

Electrical Specifications

Test Conditions: V+ = +5V, V- = -5V, V

REF

= -10V, T

A

= 25

o

C, f

CLK

= 500kHz, Unless Otherwise Noted

PARAMETER

SYMBOL

TEST

CONDITIONS

J

K

L

UNITS

MIN

TYP

MAX

MIN

TYP

MAX

MIN

TYP

MAX

AC Electrical Specifications

Test Conditions V+ = +5V, V- = -5V, T

A

= 25

o

C, f

CLK

= 500kHz, unless otherwise noted. Data

derived from extensive characterization testing. Parameters are not production tested

PARAMETER

SYMBOL

TEST

CONDITIONS

MIN

TYP

MAX

UNITS

READ CYCLE TIMING

Propagation Delay CS to Date

t

cd

RD Low, A

0

Valid

-

-

200

ns

Propagation Delay A

0

to Data

t

ad

CS Low, RD Low

-

-

200

Propagation Delay RD to Data

t

rd

CS Low, A

0

Valid

-

-

200

Propagation Delay Data to Three-State

t

rx

-

-

150

Propagation Delay EOC High to Data

t

ed

-

-

200

WRITE CYCLE TIMING

WR Low Time

t

wr

150

-

-

ns

Propagation Delay WR Low to EOC Low

t

we

Wait Mode

1

-

2

EOC High Time

t

eo

Free Run Mode

0.5

-

1.5

1/f

CLK

Conversion Time

t

conv

-

-

20

Clock Frequency Range

f

CLK

Functional Operation Only

-

500

-

kHz

NOTE:

9. All typical values have been characterized, but are not tested.

ICL7112

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICL7112LMDL | 2.0 Gbps 4x4 Crosspoint Switch 38-TSSOP -40 to 85 |

| ICL7112 | Dual LVDS Receiver 8-SOIC -40 to 85 |

| ICL7112KIDL | 12-Bit, High-Speed, CMOS uP-Compatible A/D Converter |

| ICL7112LIDL | 12-Bit, High-Speed, CMOS uP-Compatible A/D Converter |

| ICL7116CJL | 3 Digit A/D Converter With Display Hold |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICL7112LIDL | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:12-Bit, High-Speed, CMOS uP-Compatible A/D Converter |

| ICL7112LMDL | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:12-Bit, High-Speed, CMOS uP-Compatible A/D Converter |

| ICL7115 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:N-CHANNEL JFET |

| ICL7115JCDL | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:14-Bit High-Speed CMOS UP-Compatible A/D Converter |

| ICL7115JCJL | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Data Acquisition |

發(fā)布緊急采購,3分鐘左右您將得到回復。