- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385437 > HYS72T64001HR (QIMONDA) 240-Pin Registered DDR2 SDRAM Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72T64001HR |

| 廠商: | QIMONDA |

| 英文描述: | 240-Pin Registered DDR2 SDRAM Modules |

| 中文描述: | 240針DDR2 SDRAM的注冊模塊 |

| 文件頁數(shù): | 45/67頁 |

| 文件大小: | 1462K |

| 代理商: | HYS72T64001HR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

Internet Data Sheet

Rev. 1.21, 2007-03

09152006-J5FK-C565

45

HYS72T[32/64]0xxHR–[2.5/3/3S/3.7/5]–A

Registered DDR2 SDRAM Modules

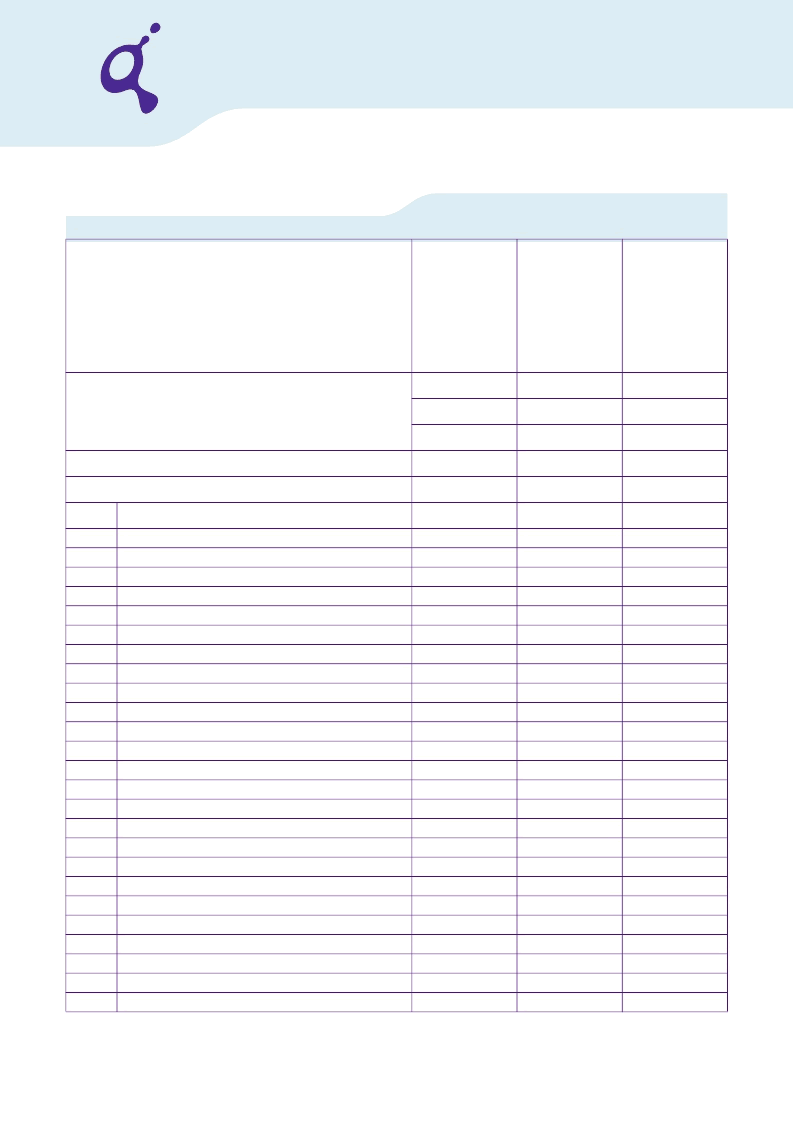

TABLE 30

SPD Codes for PC2–5300R–444

Product Type

H

H

H

Organization

256MB

512MB

512MB

×

72

×

72

×

72

1 Rank (

×

8)

1 Rank (

×

4)

2 Ranks (

×

8)

Label Code

PC2–5300R–444

PC2–5300R–444

PC2–5300R–444

JEDEC SPD Revision

Rev. 1.2

Rev. 1.2

Rev. 1.2

Byte#

Description

HEX

HEX

HEX

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Programmed SPD Bytes in EEPROM

Total number of Bytes in EEPROM

Memory Type (DDR2)

Number of Row Addresses

Number of Column Addresses

DIMM Rank and Stacking Information

Data Width

Not used

Interface Voltage Level

t

CK

@ CL

MAX

(Byte 18) [ns]

t

AC

SDRAM @ CL

MAX

(Byte 18) [ns]

Error Correction Support (non-ECC, ECC)

Refresh Rate and Type

Primary SDRAM Width

Error Checking SDRAM Width

Not used

Burst Length Supported

Number of Banks on SDRAM Device

Supported CAS Latencies

DIMM Mechanical Characteristics

DIMM Type Information

DIMM Attributes

Component Attributes

t

CK

@ CL

MAX

-1 (Byte 18) [ns]

t

AC

SDRAM @ CL

MAX

-1 [ns]

80

08

08

0D

0A

60

48

00

05

30

45

02

82

08

08

00

0C

04

38

01

01

04

03

30

45

80

08

08

0D

0B

60

48

00

05

30

45

02

82

04

04

00

0C

04

38

01

01

05

03

30

45

80

08

08

0D

0A

61

48

00

05

30

45

02

82

08

08

00

0C

04

38

01

01

05

03

30

45

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。