- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385437 > HYS72T512022ER (QIMONDA) 240-Pin Dual Die Registered DDR2 SDRAM Modules PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72T512022ER |

| 廠商: | QIMONDA |

| 英文描述: | 240-Pin Dual Die Registered DDR2 SDRAM Modules |

| 中文描述: | 240針雙模具注冊(cè)DDR2 SDRAM內(nèi)存模塊 |

| 文件頁(yè)數(shù): | 21/36頁(yè) |

| 文件大小: | 980K |

| 代理商: | HYS72T512022ER |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

Internet Data Sheet

Rev. 1.0, 2007-03

03292007-RHOW-C5L6

21

HYS72T[512/1G]0x2EP–[3S/3.7]–B

Registerd DDR2 SDRAM Module

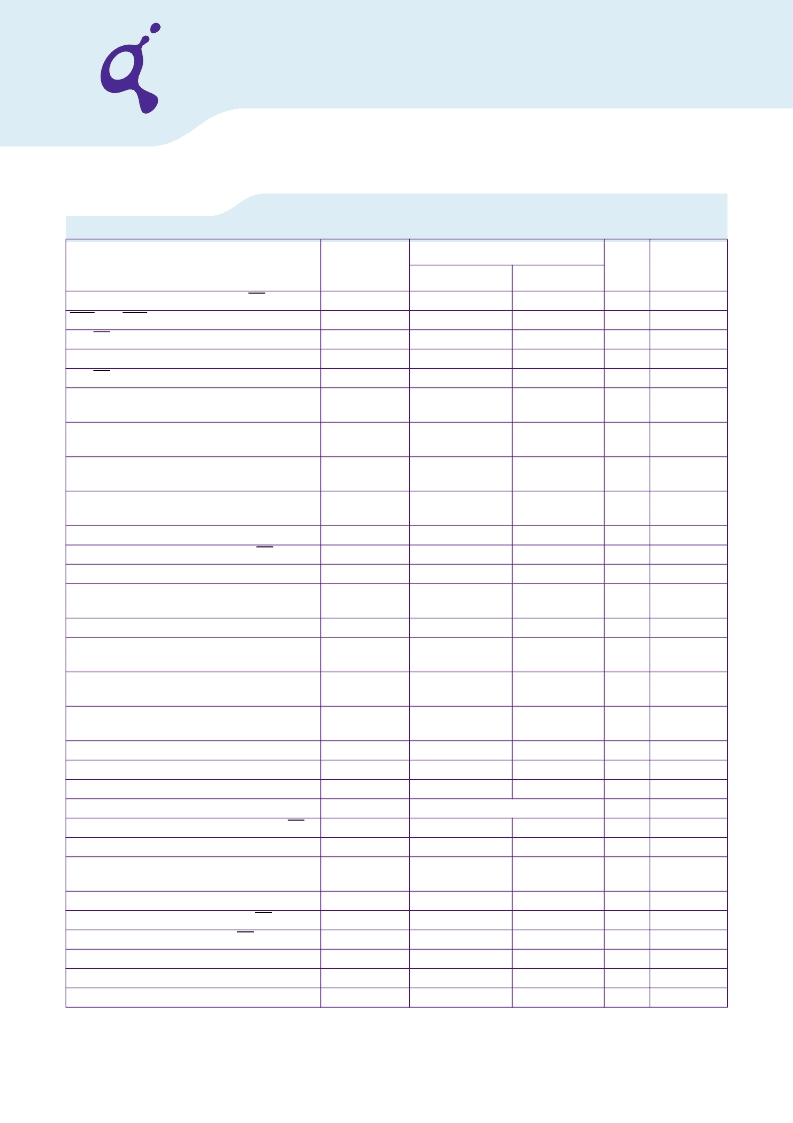

TABLE 14

DRAM Component Timing Parameter by Speed Grade - DDR2–533

Parameter

Symbol

DDR2–533

Unit

Note

1)2)3)4)5)

6)7)

Min.

Max.

DQ output access time from CK / CK

CAS A to CAS B command period

CK, CK high-level width

CKE minimum high and low pulse width

CK, CK low-level width

Auto-Precharge write recovery + precharge

time

Minimum time clocks remain ON after CKE

asynchronously drops LOW

DQ and DM input hold time (differential data

strobe)

DQ and DM input hold time (single ended data

strobe)

DQ and DM input pulse width (each input)

DQS output access time from CK / CK

DQS input low (high) pulse width (write cycle)

DQS-DQ skew (for DQS & associated DQ

signals)

Write command to 1st DQS latching transition

DQ and DM input setup time (differential data

strobe)

DQ and DM input setup time (single ended data

strobe)

DQS falling edge hold time from CK (write

cycle)

DQS falling edge to CK setup time (write cycle)

t

DSS

Four Activate Window period

Four Activate Window period

Clock half period

Data-out high-impedance time from CK / CK

Address and control input hold time

Address and control input pulse width

(each input)

Address and control input setup time

DQ low-impedance time from CK / CK

DQS low-impedance from CK / CK

Mode register set command cycle time

OCD drive mode output delay

Data output hold time from DQS

t

AC

t

CCD

t

CH

t

CKE

t

CL

t

DAL

–500

2

0.45

3

0.45

WR +

t

RP

+500

—

0.55

—

0.55

—

ps

t

CK

t

CK

t

CK

t

CK

t

CK

—

—

—

—

—

8)18)

t

DELAY

t

IS

+

t

CK

+

t

IH

—

ns

9)

t

DH

(base)

225

—

ps

10)

t

DH1

(base)

–25

—

ps

11)

t

DIPW

t

DQSCK

t

DQSL,H

t

DQSQ

0.35

–450

0.35

—

—

+

450

—

300

t

CK

ps

t

CK

ps

—

—

—

11)

t

DQSS

t

DS

(base)

– 0.25

100

+ 0.25

—

t

CK

ps

—

11)

t

DS1

(base)

–25

—

ps

11)

t

DSH

0.2

—

t

CK

—

0.2

37.5

50

MIN. (

t

CL,

t

CH

)

—

375

0.6

—

—

—

t

CK

ns

ns

—

ps

ps

t

CK

—

—

t

FAW

t

FAW

t

HP

t

HZ

t

IH

(base)

t

IPW

13)

12)

t

AC.MAX

—

—

13)

11)

—

t

IS

(base)

t

LZ(DQ)

t

LZ(DQS)

t

MRD

t

OIT

t

QH

250

2

×

t

AC.MIN

t

AC.MIN

2

0

t

HP

–

t

QHS

—

t

AC.MAX

t

AC.MAX

—

12

—

ps

ps

ps

t

CK

ns

—

11)

14)

14)

—

—

—

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72T512022HFN-3.7-A | 240-Pin Fully-Buffered DDR2 SDRAM Modules DDR2 SDRAM |

| HYS72T512122HFN-3.7-A | 240-Pin Fully-Buffered DDR2 SDRAM Modules DDR2 SDRAM |

| HYS72T512341HKP-3.7-B | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T512341HKP-5-B | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T512341HHP | 240-Pin Registered DDR2 SDRAM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T512022HFN-3.7-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Fully-Buffered DDR2 SDRAM Modules DDR2 SDRAM |

| HYS72T512022HR | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T512022HR-3.7-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T512022HR-3S-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T512022HR-5-A | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。