- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385437 > HYS72T32000HU-2.5-A (QIMONDA AG) 240-Pin Unbuffered DDR2 SDRAM Modules PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72T32000HU-2.5-A |

| 廠商: | QIMONDA AG |

| 元件分類(lèi): | DRAM |

| 英文描述: | 240-Pin Unbuffered DDR2 SDRAM Modules |

| 中文描述: | 32M X 72 DDR DRAM MODULE, 0.4 ns, DMA240 |

| 封裝: | GREEN, DIMM-240 |

| 文件頁(yè)數(shù): | 24/73頁(yè) |

| 文件大小: | 1574K |

| 代理商: | HYS72T32000HU-2.5-A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)

Internet Data Sheet

Rev. 1.41, 2006-11

03062006-0GN5-WTPW

24

HYS[64/72]T[16/32/64]0xxHU–[2.5/../5]–A

Unbuffered DDR2 SDRAM Modules

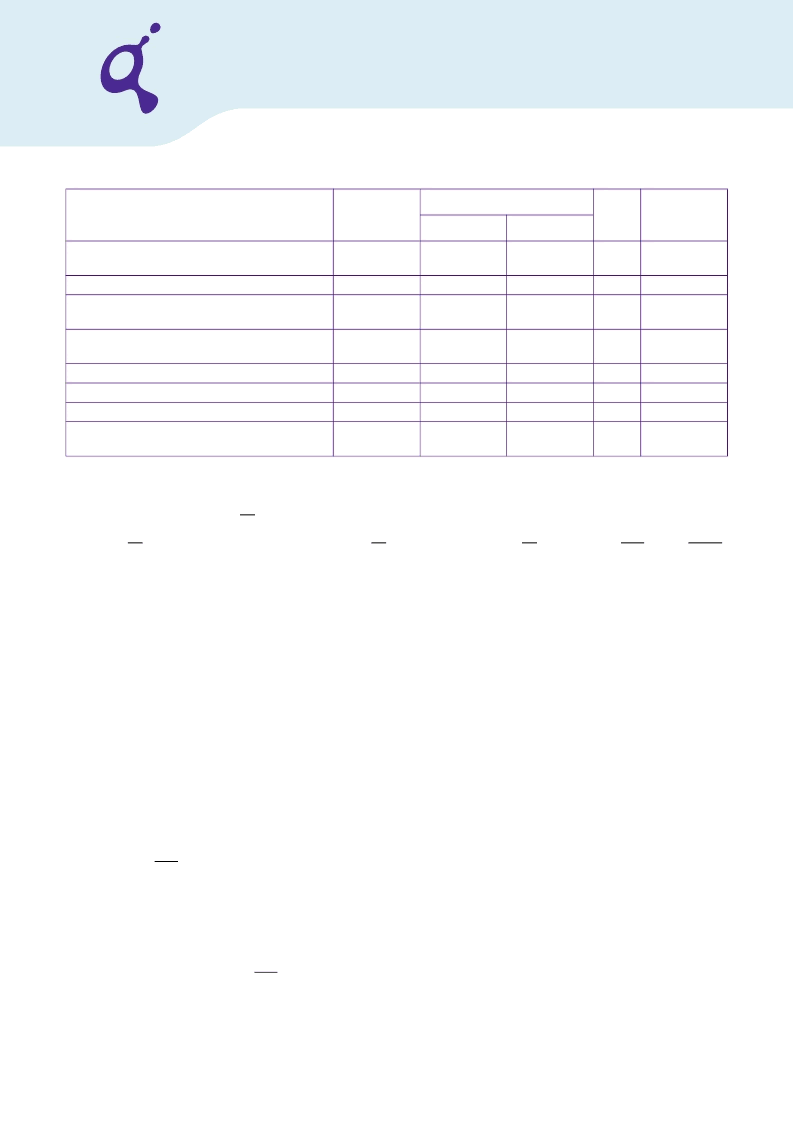

Exit precharge power-down to any valid

command (other than NOP or Deselect)

Exit power down to read command

Exit active power-down mode to read command

(slow exit, lower power)

CKE minimum pulse width ( high and low pulse

width)

Mode register set command cycle time

MRS command to ODT update delay

OCD drive mode output delay

Minimum time clocks remain ON after CKE

asynchronously drops LOW

1) For details and notes see the relevant Qimonda component data sheet

2)

V

DDQ

= 1.8 V ± 0.1V;

V

DD

= 1.8 V ± 0.1 V. See notes

5)6)7)8)

3) Timing that is not specified is illegal and after such an event, in order to guarantee proper operation, the DRAM must be powered down

and then restarted through the specified initialization sequence before normal operation can continue.

4) Timings are guaranteed with CK/CK differential Slew Rate of 2.0 V/ns. For DQS signals timings are guaranteed with a differential Slew

Rate of 2.0 V/ns in differential strobe mode and a Slew Rate of 1 V/ns in single ended mode.

5) The CK / CK input reference level (for timing reference to CK / CK) is the point at which CK and CK cross. The DQS / DQS, RDQS / RDQS,

input reference level is the crosspoint when in differential strobe mode.

6) Inputs are not recognized as valid until

V

REF

stabilizes. During the period before

V

REF

stabilizes, CKE = 0.2 x

V

DDQ

is recognized as low.

7) The output timing reference voltage level is

V

TT

.

8) New units, ‘

t

CK.AVG

‘ and ‘nCK‘, are introduced in DDR2–667 and DDR2–800. Unit ‘

t

CK.AVG

‘ represents the actual

t

CK.AVG

of the input clock

under operation. Unit ‘nCK‘ represents one clock cycle of the input clock, counting the actual clock edges. Note that in DDR2–400 and

DDR2–533, ‘

t

CK

‘ is used for both concepts. Example:

t

XP

= 2 [nCK] means; if Power Down exit is registered at Tm, an Active command

may be registered at Tm + 2, even if (Tm + 2 - Tm) is 2 x

t

CK.AVG

+

t

ERR.2PER(Min)

.

9) When the device is operated with input clock jitter, this parameter needs to be derated by the actual

t

ERR(6-10per)

of the input clock. (output

deratings are relative to the SDRAM input clock.) For example, if the measured jitter into a DDR2–667 SDRAM has

t

ERR(6-10PER).MIN

= – 272

ps and

t

ERR(6- 10PER).MAX

= + 293 ps, then

t

DQSCK.MIN(DERATED)

=

t

DQSCK.MIN

–

t

ERR(6-10PER).MAX

= – 400 ps – 293 ps = – 693 ps and

t

DQSCK.MAX(DERATED)

DQSCK.MAX

–

t

ERR(6-10PER).MIN

t

LZ.DQ

for DDR2–667 derates to

t

LZ.DQ.MIN(DERATED)

= - 900 ps – 293 ps = – 1193 ps and

t

LZ.DQ.MAX(DERATED)

= 450 ps + 272 ps = + 722 ps. (Caution on the MIN/MAX usage!)

10) Input clock jitter spec parameter. These parameters are referred to as 'input clock jitter spec parameters' and these parameters apply to

DDR2–667 and DDR2–800 only. The jitter specified is a random jitter meeting a Gaussian distribution.

11) These parameters are specified per their average values, however it is understood that the relationship between the average timing and

the absolute instantaneous timing holds all the times (min. and max of SPEC values are to be used for calculations ).

12) Input waveform timing

t

DS

with differential data strobe enabled MR[bit10] = 0, is referenced from the input signal crossing at the

V

IH.AC

level

to the differential data strobe crosspoint for a rising signal, and from the input signal crossing at the

V

IL.AC

level to the differential data strobe

crosspoint for a falling signal applied to the device under test. DQS, DQS signals must be monotonic between

V

il(DC)MAX

and

V

ih(DC)MIN

. See

Figure 4

.

13) If

t

DS

or

t

DH

is violated, data corruption may occur and the data must be re-written with valid data before a valid READ can be executed.

14) These parameters are measured from a data signal ((L/U)DM, (L/U)DQ0, (L/U)DQ1, etc.) transition edge to its respective data strobe signal

((L/U/R)DQS / DQS) crossing.

15) Input waveform timing

t

DH

with differential data strobe enabled MR[bit10] = 0, is referenced from the differential data strobe crosspoint to

the input signal crossing at the

V

level for a falling signal and from the differential data strobe crosspoint to the input signal crossing

at the

V

IL.DC

level for a rising signal applied to the device under test. DQS, DQS signals must be monotonic between

V

IL.DC.MAX

and

V

IH.DC.MIN

. See

Figure 4

.

16)

t

HZ

and

t

LZ

transitions occur in the same access time as valid data transitions. These parameters are referenced to a specific voltage level

which specifies when the device output is no longer driving (

t

HZ

), or begins driving (

t

LZ

) .

17)

t

DQSQ

: Consists of data pin skew and output pattern effects, and p-channel to n-channel variation of the output drivers as well as output

slew rate mismatch between DQS / DQS and associated DQ in any given cycle.

t

XP

2

—

nCK

t

XARD

t

XARDS

2

7 – AL

—

—

nCK

nCK

t

CKE

3

—

nCK

31)

t

MRD

t

MOD

t

OIT

t

DELAY

2

0

0

t

IS

+

t

CK .AVG

+

t

IH

—

12

12

—

nCK

ns

ns

ns

28)

28)

Parameter

Symbol

DDR2–667

Unit

Note

1)2)3)4)5)6)7)

8)

Min.

Max.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72T32000HU-25F-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-3.7-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-3-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-3S-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-5-A | 240-Pin Unbuffered DDR2 SDRAM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T32000HU-25F-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-3.7-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-3-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-3S-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

| HYS72T32000HU-5-A | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:240-Pin Unbuffered DDR2 SDRAM Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。