- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385436 > HYS72T1G242EP-3.7-C (QIMONDA AG) 240-Pin Dual Die Registered DDR2 SDRAM Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72T1G242EP-3.7-C |

| 廠商: | QIMONDA AG |

| 元件分類: | DRAM |

| 英文描述: | 240-Pin Dual Die Registered DDR2 SDRAM Modules |

| 中文描述: | 1G X 72 DDR DRAM MODULE, 0.7 ns, DMA240 |

| 封裝: | GREEN, RDIMM-240 |

| 文件頁數(shù): | 24/43頁 |

| 文件大小: | 1309K |

| 代理商: | HYS72T1G242EP-3.7-C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

Internet Data Sheet

Rev. 1.0, 2007-07

07242007-LR08-OZC0

24

HYS72T1G242EP–[25F/2.5/3/3S/3.7]–C

Registerd DDR2 SDRAM Module

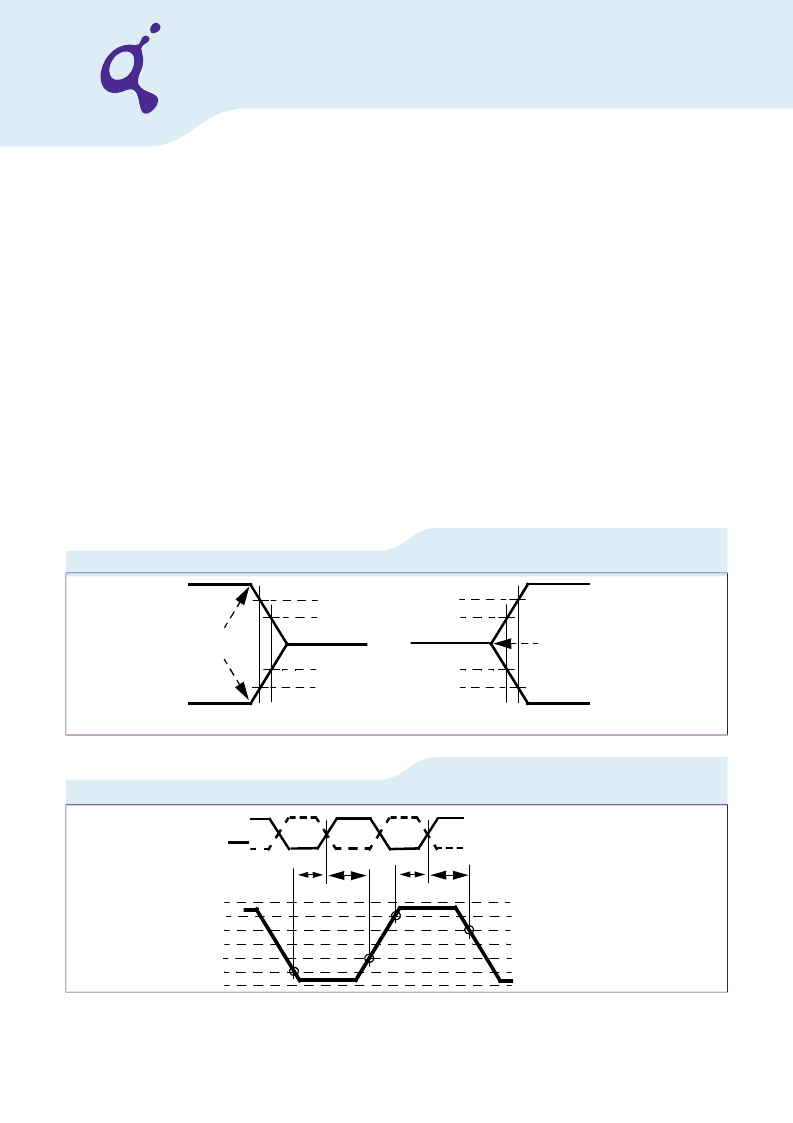

FIGURE 2

Method for calculating transitions and endpoint

FIGURE 3

Differential input waveform timing -

t

DS

and

t

DS

28) The Auto-Refresh command interval has be reduced to 3.9

μ

s when operating the DDR2 DRAM in a temperature range between 85

°

C

and 95

°

C.

29) 0 °C

≤

T

CASE

≤

85

°

C

30) 85

°

C

<

T

CASE

≤

95

°

C

31) A maximum of eight Auto-Refresh commands can be posted to any given DDR2 SDRAM device.

32)

t

RPST

end point and

t

RPRE

begin point are not referenced to a specific voltage level but specify when the device output is no longer driving

(

), or begins driving (

t

).

Figure 2

shows a method to calculate these points when the device is no longer driving (

t

), or begins

driving (

t

) by measuring the signal at two different voltages. The actual voltage measurement points are not critical as long as the

calculation is consistent.

33) When the device is operated with input clock jitter, this parameter needs to be derated by the actual

t

of the input clock. (output

deratings are relative to the SDRAM input clock.) For example, if the measured jitter into a DDR2–667 SDRAM has

t

JIT.PER.MIN

= – 72 ps

and

t

JIT.PER.MAX

= + 93 ps, then

t

=

t

+

t

= 0.9 x

t

– 72 ps = + 2178 ps and

t

RPRE.MAX(DERATED)

=

t

RPRE.MAX

+

t

JIT.PER.MAX

t

CK.AVG

+ 93 ps = + 2843 ps. (Caution on the MIN/MAX usage!).

34) When the device is operated with input clock jitter, this parameter needs to be derated by the actual

t

of the input clock. (output

deratings are relative to the SDRAM input clock.) For example, if the measured jitter into a DDR2–667 SDRAM has

t

JIT.DUTY.MIN

= – 72 ps

and

t

JIT.DUTY.MAX

= + 93 ps, then

t

RPST.MIN(DERATED)

=

t

RPST.MIN

+

t

JIT.DUTY.MIN

= 0.4 x

t

CK.AVG

– 72 ps = + 928 ps and

t

RPST.MAX(DERATED)

=

t

RPST.MAX

+

t

JIT.DUTY.MAX

= 0.6 x

t

CK.AVG

+ 93 ps = + 1592 ps. (Caution on the MIN/MAX usage!).

35) For these parameters, the DDR2 SDRAM device is characterized and verified to support

t

nPARAM

= RU{

t

PARAM

/

t

CK.AVG

}, which is in clock

cycles, assuming all input clock jitter specifications are satisfied. For example, the device will support

t

nRP

= RU{

/

t

}, which is in

clock cycles, if all input clock jitter specifications are met. This means: For DDR2–667 5–5–5, of which

t

= 15 ns, the device will support

t

nRP

= RU{

t

RP

/

t

CK.AVG

} = 5, i.e. as long as the input clock jitter specifications are met, Precharge command at Tm and Active command at

Tm + 5 is valid even if (Tm + 5 - Tm) is less than 15 ns due to input clock jitter.

36)

t

WTR

is at lease two clocks (2 x

t

CK

) independent of operation frequency.

W+=

W5367

HQGSR LQW

7 7

92+[P

9

92+[P

9

92/ [P

9

92/ [P 9

W/=

W535(

EHJLQSRLQW

7

7

977 [P9

977 [P9

977 [ P9

977 [P9

W/= W535(

EHJLQSRL QW

7 7

W+=W53 67

HQGSRL QW

7 7

W'6

9

''4

9

,+D F

PL Q

9

,+G F

PL Q

6

2%&DC

9

,/ GF

PD [

9

,/ DF

PD [

9

66

'46

'46

W'+

W'6

W'+

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72T1G242EP-3-C | 240-Pin Dual Die Registered DDR2 SDRAM Modules |

| HYS72T1G242EP-3S-C | 240-Pin Dual Die Registered DDR2 SDRAM Modules |

| HYS72T256000ER | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256000ER-3.7-B | 240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256000ER-5-B | 240-Pin Registered DDR2 SDRAM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72T1G242EP-3-C | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Dual Die Registered DDR2 SDRAM Modules |

| HYS72T1G242EP-3S-C | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Dual Die Registered DDR2 SDRAM Modules |

| HYS72T256000ER | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256000ER-3.7-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

| HYS72T256000ER-5-B | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:240-Pin Registered DDR2 SDRAM Modules |

發(fā)布緊急采購,3分鐘左右您將得到回復。