- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385427 > HY5DU56822ELFP-D43 (Hynix Semiconductor Inc.) 256Mb DDR SDRAM PDF資料下載

參數(shù)資料

| 型號: | HY5DU56822ELFP-D43 |

| 廠商: | Hynix Semiconductor Inc. |

| 英文描述: | 256Mb DDR SDRAM |

| 中文描述: | 256Mb的DDR SDRAM內(nèi)存 |

| 文件頁數(shù): | 22/29頁 |

| 文件大小: | 260K |

| 代理商: | HY5DU56822ELFP-D43 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

Rev. 1.1 / J une 2006

22

1

HY5DU56822E(L)FP

HY5DU561622E(L)FP

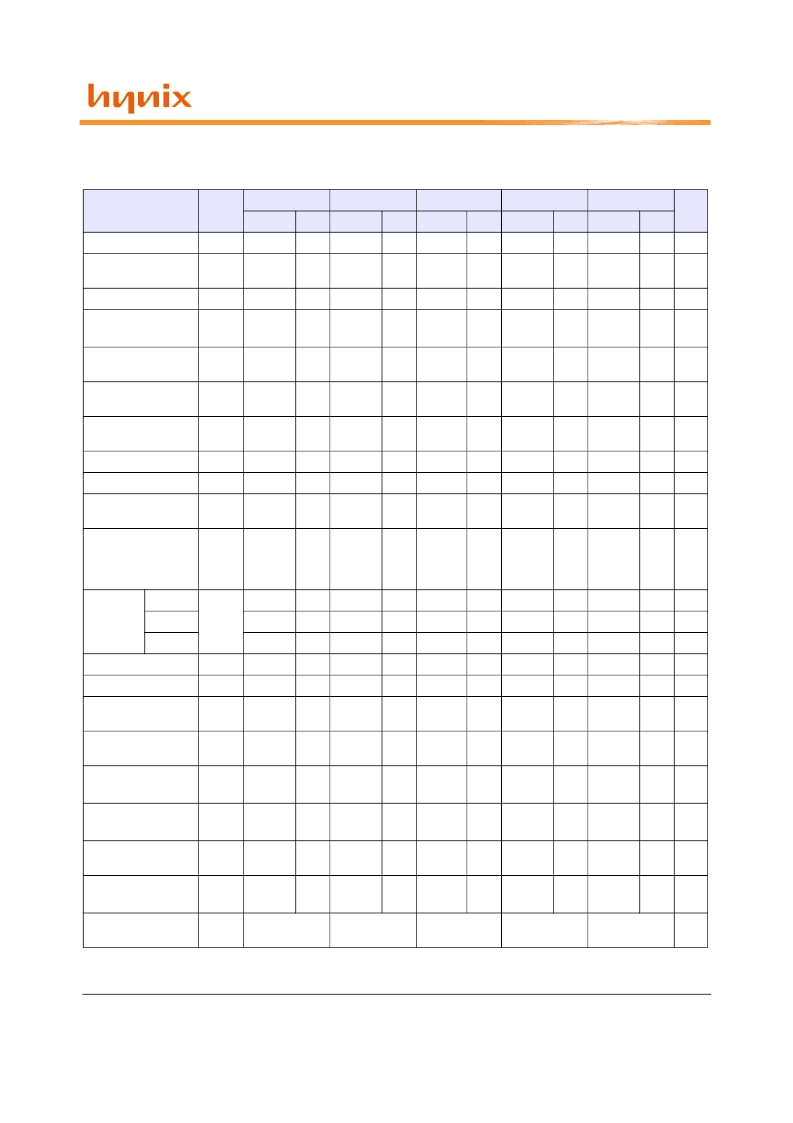

AC CHARACTERISTICS

(note: 1 - 9 / AC operating conditions unless otherwise noted)

Parameter

Symbol

DDR400B

DDR333

DDR266A

DDR266B

DDR200

UNIT

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Row Cycle Time

tRC

55

-

60

-

65

-

65

-

70

-

ns

Auto Refresh Row

Cycle Time

tRFC

70

-

72

-

75

-

75

-

80

-

ns

Row Active Time

tRAS

40

70K

42

70K

45

120K

45

120K

50

120K

ns

Active to Read with

Auto Precharge Delay

tRAP

tRCD or

tRASmin

-

tRCD or

tRASmin

-

tRCD or

tRASmin

-

tRCD or

tRASmin

-

tRCD or

tRASmin

-

ns

Row Address to

Column Address Delay

tRCD

15

-

18

-

20

-

20

-

20

-

ns

Row Active to Row

Active Delay

tRRD

10

-

12

-

15

-

15

-

15

-

ns

Column Address to

Column Address Delay

tCCD

1

-

1

-

1

-

1

-

1

-

tCK

Row Precharge Time

tRP

15

-

18

-

20

-

20

-

20

-

ns

Write Recovery Time

tWR

15

-

15

-

15

-

15

-

15

-

ns

Internal Write to Read

Command Delay

tWTR

2

-

1

-

1

-

1

-

1

-

tCK

Auto Precharge Write

Recovery + Precharge

Time

22

tDAL

(tWR/

tCK)

+

(tRP/tCK)

-

(tWR/

tCK)

+

(tRP/tCK)

-

(tWR/

tCK)

+

(tRP/tCK)

-

(tWR/

tCK)

+

(tRP/tCK)

-

(tWR/

tCK)

+

(tRP/tCK)

-

tCK

System

Clock Cycle

Time

24

CL = 3

tCK

5

10

-

-

-

-

-

-

-

-

ns

CL = 2.5

6

12

6

12

7.5

12

7.5

12

8.0

12

ns

CL = 2

7.5

12

7.5

12

7.5

12

10

12

10

12

ns

Clock High Level Width

tCH

0.45

0.55

0.45

0.55

0.45

0.55

0.45

0.55

0.45

0.55

tCK

Clock Low Level Width

tCL

0.45

0.55

0.45

0.55

0.45

0.55

0.45

0.55

0.45

0.55

tCK

Data-Out edge to Clock

edge Skew

tAC

-0.7

0.7

-0.7

0.7

-0.75

0.75

-0.75

0.75

-0.75

0.75

ns

DQS-Out edge to Clock

edge Skew

tDQSCK

-0.55

0.55

-0.6

0.6

-0.75

0.75

-0.75

0.75

-0.75

0.75

ns

DQS-Out edge to Data-

Out edge Skew

21

tDQSQ

-

0.4

-

0.4

-

0.5

-

0.5

-

0.6

ns

Data-Out hold time

from DQS

20

tQH

tHP

-tQHS

-

tHP

-tQHS

-

tHP

-tQHS

-

tHP

-tQHS

-

tHP

-tQHS

-

ns

Clock Half Period

19,20

tHP

min

(tCL,tCH)

-

min

(tCL,tCH)

-

min

(tCL,tCH)

-

min

(tCL,tCH)

-

min

(tCL,tCH)

-

ns

Data Hold Skew

Factor

20

tQHS

-

0.5

-

0.5

-

0.75

-

0.75

-

0.75

ns

Valid Data Output

Window

tDV

tQH-tDQSQ

tQH-tDQSQ

tQH-tDQSQ

tQH-tDQSQ

tQH-tDQSQ

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5DU56822ELFP-H | 256Mb DDR SDRAM |

| HY5DU56822ELFP-J | 256Mb DDR SDRAM |

| HY5DU56822ELFP-K | 256Mb DDR SDRAM |

| HY5DU56822ELFP-L | 256Mb DDR SDRAM |

| HY5DV281622DT | 128M(8Mx16) GDDR SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5DU56822ELFP-H | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

| HY5DU56822ELFP-J | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

| HY5DU56822ELFP-K | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

| HY5DU56822ELFP-L | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

| HY5DU56822FLTP-D43 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:256Mb DDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。