- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1923 > HSP43168JC-33Z (Intersil)IC FIR FILTER DUAL 84-PLCC PDF資料下載

參數(shù)資料

| 型號: | HSP43168JC-33Z |

| 廠商: | Intersil |

| 文件頁數(shù): | 2/25頁 |

| 文件大小: | 0K |

| 描述: | IC FIR FILTER DUAL 84-PLCC |

| 標(biāo)準(zhǔn)包裝: | 15 |

| 濾波器類型: | FIR |

| 濾波器數(shù): | 2 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 84-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 84-PLCC(29.21x29.21) |

| 包裝: | 管件 |

10

FN2808.12

July 27, 2009

Input/Output Formats

The Dual FIR supports mixed mode arithmetic with both

unsigned and two's complement data and coefficients. The

input and output formats for both data types are shown in

Figure 3. If the Dual FIR is configured as an even symmetric

filter with unsigned data and coefficients, the output will be

unsigned. Otherwise, the output will be two's complement.

The MUX/Adder can be configured to implement

programmable rounding at bit locations 2-10 through 21. The

round is implemented by adding a 1 to the specified location

example, to configure the part such that the output is

rounded to the 10 MSBs, OUT18 - 27, the round position

would be chosen to be 2-1. The negative sign on the MSB

indicates 2’s complement format.

Application Examples

In this section a number of examples are presented which

detail even, odd, symmetric, asymmetric, decimating and

dual FIR filter configurations. These examples are intended

to illustrate the different operational features of the

HSP43168 and should be used as a guide in developing an

application specific filter configuration. Use Table 6 to select

and find the example that best matches your application.

Examples 1 through 5 are explained using a single four tap

FIR cell, but the same concept applies to FIR filters which

use both FIR cells (A and B) in a single filter configuration.

Example 6 details a dual filter mode where FIR cell A and B

implement different digital filters. All examples are

functionally verified configurations. Each example details a

complete design solution, including a block diagram, a

data/coefficient alignment illustration, a data flow diagram

and a control signal timing diagram.

INPUT DATA FORMAT INA0-9, INB0-9

FRACTIONAL TWO’S COMPLEMENT

9876543210

-20

.2-1

2-2

2-3

2-4

2-5

2-6

2-7

2-8

2-9

OUTPUT DATA FORMAT OUT9-27

FRACTIONAL TWO'S COMPLEMENT

27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

-29 28 27 26 25 24 23 22 21 20 .2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9

OUTPUT DATA FORMAT OUT0-8

FRACTIONAL TWO'S COMPLEMENT

876543210

2-10

2-11

2-12

2-13

2-14

2-15

2-16

2-17

2-18

INPUT DATA FORMAT INA0-9, INB0-9

FRACTIONAL UNSIGNED

9876543210

20

.2-1

2-2

2-3

2-4

2-5

2-6

2-7

2-8

2-9

OUTPUT DATA FORMAT OUT9-27

FRACTIONAL UNSIGNED

27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

29 28 27 26 25 24 23 22 21 20 .2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9

OUTPUT DATA FORMAT OUT0-8

FRACTIONAL UNSIGNED

876543210

2-10

2-11

2-12

2-13

2-14

2-15

2-16

2-17

2-18

FIGURE 3. INPUT/OUTPUT FORMAT DEFINITIONS

TABLE 6. FILTER EXAMPLE SELECTION GUIDE

FILTER TYPE

EXAMPLE NUMBER

Even Tap Even Symmetric

1

Odd Tap Even Symmetric

2

Asymmetric

3

Even Tap Decimating

4

Odd Tap Decimating

5

Dual Decimating

6

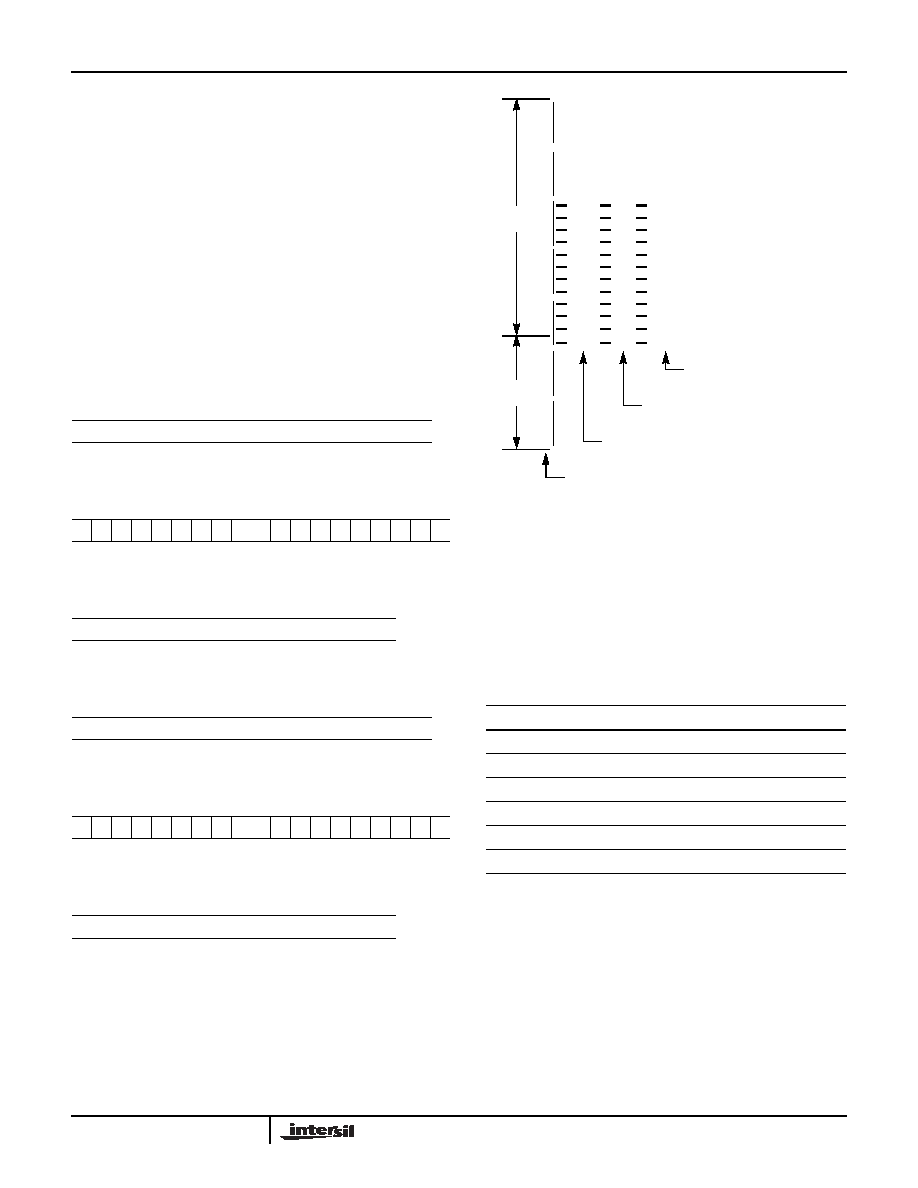

FIGURE 4. ROUND POSITION BIT DEFINITION

IOUT

9-27

IOUT

0-8

21

20

2-1

2-2

2-3

2-4

2-5

2-6

2-7

2-8

2-9

2-10

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

19

18

17

16

15

14

13

12

11

10

9

8

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

“ROUND POSITION” VALUE

NUMBER OF OUTPUT BITS

LOCATION OF ADDITION OF 1

OUTPUT BITS

HSP43168

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP43216JC-52Z | IC HALFBAND FILTER 84-PLCC |

| HSP43220JC-33Z | IC DECIMATING DGTL FILTER 84PLCC |

| IA188EM-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

| IA188ES-PTQ100I-R-03 | IC MCU 8/16BIT 40MHZ 100TQFP |

| IA6805E2PLC44IR0 | IC MCU 8BIT 5MHZ 44PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP43168JC-40 | 制造商:Rochester Electronics LLC 功能描述:DUAL DIGITAL FILTER 84 PLCC, 40MHZ, COMM - Bulk |

| HSP43168JC-45 | 制造商:Rochester Electronics LLC 功能描述:DUAL DIGITAL FILTER 84 PLCC, 45MHZ, COMM - Bulk |

| HSP43168JC-45S5001 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP43168JI-40 | 制造商:Rochester Electronics LLC 功能描述:DUAL DIGITAL FILTER 84 PLCC 40MHZ,INDUSTRIAL TEMP - Bulk |

| HSP43168VC-33 | 制造商:Rochester Electronics LLC 功能描述:DUAL DIGITAL FILTER 100 PQFP, 33MHZ, COMM - Bulk 制造商:Harris Corporation 功能描述: 制造商:Intersil Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。