- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383073 > HMC106 SPDT RF Reflective Switch PDF資料下載

參數(shù)資料

| 型號: | HMC106 |

| 英文描述: | SPDT RF Reflective Switch |

| 中文描述: | 擲射頻反射開關(guān) |

| 文件頁數(shù): | 9/15頁 |

| 文件大小: | 190K |

| 代理商: | HMC106 |

HMC10XX FAMILY

9

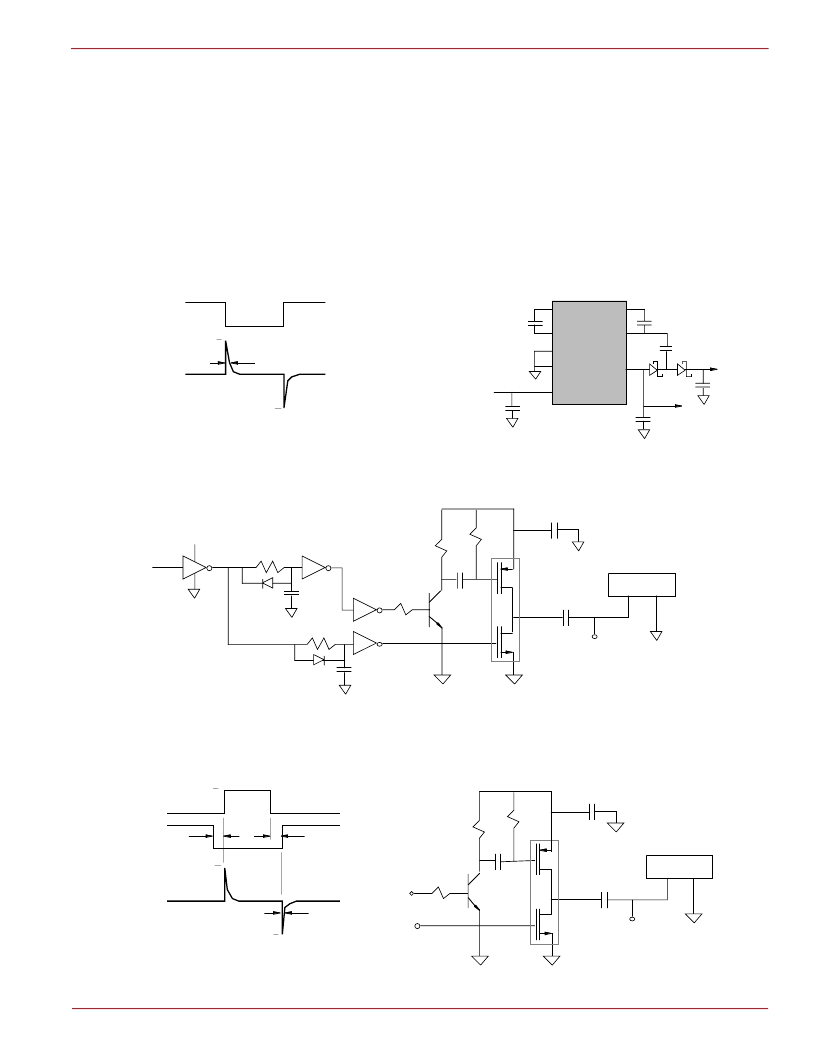

Single Clock Circuitry—Some form of clock is needed to

trigger the set and reset pulses (Figure 5) to create the

switching signal. The circuit shown in Figure 7 can be used

to create a strong (>4Amp) pulse. The diodes, resistors,

capacitors and inverters basically create the TRS and the

TSR delays. Now a single signal (Clock) can trigger a set or

reset pulse. The minimum timing between the rising and

falling edges of Clock are determined by the 25K

and 1nF

time constant. That is, the minimum high and low time for

Clock is

≈

25

μ

s.

Micro Processor—The circuit in Figure 8 generates a strong

set/reset pulse (>4 Amp) under microprocessor control. The

T

SR

T

RS

SET

RESET

S/R

16V

-16V

T

RS

≥

5 μsec

T

SR

≥

5 μsec

T

PW

≈

2 μsec

5V

T

PW

set

reset

S/R strap @ 4.5

typ.

3A peak (min.)

SET

10K

1

0.22μF

4.7μF (1)

25K

+16 to 20V

17

HMC2003

2N3904

RESET

S/R

I

1

2

4

3

5,6

7,8

(1) Tantalum, low R

(2) HEXFETs with

≈

0.2

Ron

25K

0.1μF

Figure 8—Set/Reset Circuit With Microprocessor Control(1001/1002)

SET and RESET signals are generated from a

microprocessor and control the P and N channel HEXFET

drivers (IRF7106). The purpose of creating the TRS and the

TSR delays are to make sure that one HEXFET is off before

the other one turns on. Basically, a break-before-make

switching pattern. The current pulse is drawn from the 4.7

μ

F

capacitor. If the 5V to 20V converter is used as shown in

Figure 6, then the resultant noise and droop on the 16-20V

supply is not an issue. But if the 16-20V supply is used

elsewhere in the system, then a series dropping resistor

(

≈

500

) should be placed between the 4.7

μ

F capacitor and

the supply.time constant. That is, the minimum high and low

time for Clock is

≈

25

μ

s.

MAX662A

Clock

S/R

16V

-16V

T

PW

≈

2 μsec

5V

set

reset

Figure 5—Single Clock Set/Reset Timing

Figure 6—5V to 20V Converter

0.22μF*

1

2

8

7

5

SHDN

GND

Vcc

C1-

C1+

1μF

Vout

4

3

C2+

C2-

0.22μF*

1μF

1N5818

20V

6

5V

* Use tantalum capacitors

12V

2μF

1μF

10K

25K

+16 to 20V

2N3904

25K

0.1μF

S/R strap @ 4.5

typ.

3A peak (min.)

Clock

1

0.22μF (2)

4.7μF (3)

17

HMC2003

S/R

(1) HEXFETs with

≈

0.2

Ron

(2) 0.22μF Tantalum or a

0.68 μF Ceramic CK06

(3) Tantalum, low R

25K

25K

1nF

1nF

8

9

4

3

2

1

6

5

7

14

5V

74HC04

1N4001

I

1

2

4

3

5,6

7,8

Figure 7—Single Clock Set/Reset Pulse Circuit (1001/1002)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMC109 | Analog Attenuator |

| HMC160QS16 | Interface IC |

| HMC160S14 | Interface IC |

| HMC162C8 | Analog IC |

| HMC167SS8 | Interface IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMC1060LP3E | 制造商:Hittite Microwave Corp 功能描述:IC REG LDO ADJ 16SMT |

| HMC1060LP3ETR | 制造商:Hittite Microwave Corp 功能描述:HMC1060 Series Quad Output 500 mA Linear Voltage Regulator - 3x3 mm QFN-16 |

| HMC1061LC5 | 制造商:Hittite Microwave Corp 功能描述:IC AMP TRACK&HOLD 4GS/S 32SMD |

| HMC1063LP3E | 制造商:Hittite Microwave Corp 功能描述:IC MMIC IQ MIXER GAAS 16SMD |

| HMC1065LP4E | 制造商:Hittite Microwave Corp 功能描述:IC MMIC IQ DOWNCONV 24SMD |

發(fā)布緊急采購,3分鐘左右您將得到回復。