- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299028 > EMC2103-1-KP-TR (STANDARD MICROSYSTEMS CORP) PDF資料下載

參數(shù)資料

| 型號(hào): | EMC2103-1-KP-TR |

| 廠商: | STANDARD MICROSYSTEMS CORP |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, QCC12 |

| 封裝: | 4 X 4 MM, ROHS COMPLIANT, QFN-12 |

| 文件頁數(shù): | 47/89頁 |

| 文件大?。?/td> | 1243K |

| 代理商: | EMC2103-1-KP-TR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁當(dāng)前第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

SMSC EMC2103

51

Revision 0.90 (08-19-08)

DATASHEET

6.10

Configuration Register

The Configuration Register controls the basic functionality of the EMC2103. The bits are described

below.

Bit 7 - MASK - Blocks the ALERT pin from being asserted.

‘0’ (default) - The ALERT pin is unmasked. If any bit in either status register is set, the ALERT pin

will be asserted (unless individually masked via the Mask Register)

‘1’ - The ALERT pin is masked and will not be asserted.

Bit 3 - SYS3 (EMC2103-2 only) - Enables the high temperature limit for the External Diode 3 channel

to trigger the Critical / Thermal Shutdown circuitry (see Section 5.1).

‘0’ (default) - the External Diode 3 channel high limit will not be linked to the SYS_SHDN pin. If the

temperature meets or exceeds the limit, the ALERT pin will be asserted normally.

‘1’ - the External Diode 3 channel high limit will be linked to the SYS_SHDN pin. If the temperature

meets or exceeds the limit then the SYS_SHDN pin will be asserted. The SYS_SHDN# pin will be

released when the temperature drops below the high limit. The ALERT pin will be asserted

normally.

Bit 2 - SYS2 (EMC2103-2 only) - Enables the high temperature limit for the External Diode 2 channel

to trigger the Critical / Thermal Shutdown circuitry (see Section 5.1).

‘0’ (default) - the External Diode 2 channel high limit will not be linked to the SYS_SHDN pin. If the

temperature meets or exceeds the limit, the ALERT pin will be asserted normally.

‘1’ - the External Diode 2 channel high limit will be linked to the SYS_SHDN pin. If the temperature

meets or exceeds the limit then the SYS_SHDN pin will be asserted. The ALERT pin will be

asserted normally.

Bit 1 - SYS1 - Enables the high temperature limit for the External Diode 1 channel to trigger the Critical

/ Thermal Shutdown circuitry (see Section 5.1).

‘0’ (default) - The External Diode 1 channel high limit will not be linked to the SYS_SHDN pin. If

the temperature meets or exceeds the limit, the ALERT pin will be asserted normally.

‘1’ - The External Diode 1 channel high limit will be linked to the SYS_SHDN pin. If the temperature

meets or exceeds the limit then the SYS_SHDN pin will be asserted. The ALERT pin will be

asserted normally.

Bit 0 - APD (EMC2103-2 only) - This bit enables the Anti-parallel diode functionality on the External

Diode 3 pins (DP3 and DN3).

‘0’ (default) - The Anti-parallel diode functionality is disabled. The External Diode 2 channel can be

configured for any type of diode

‘1’ - The Anti-parallel diode functionality is enabled. Both the External Diode 2 and 3 channels are

configured to support a diode or diode connected transistor (such as a 2N3904).

APPLICATION NOTE: When the APD diode is enabled, there will be a delay of a full temperature update before

any comparisons and functionality associated with the External Diode 3 channel will be

implemented. This includes the SYS3 bit operation, limit comparisons, and look up table

comparisons.

The Configuration Register is software locked.

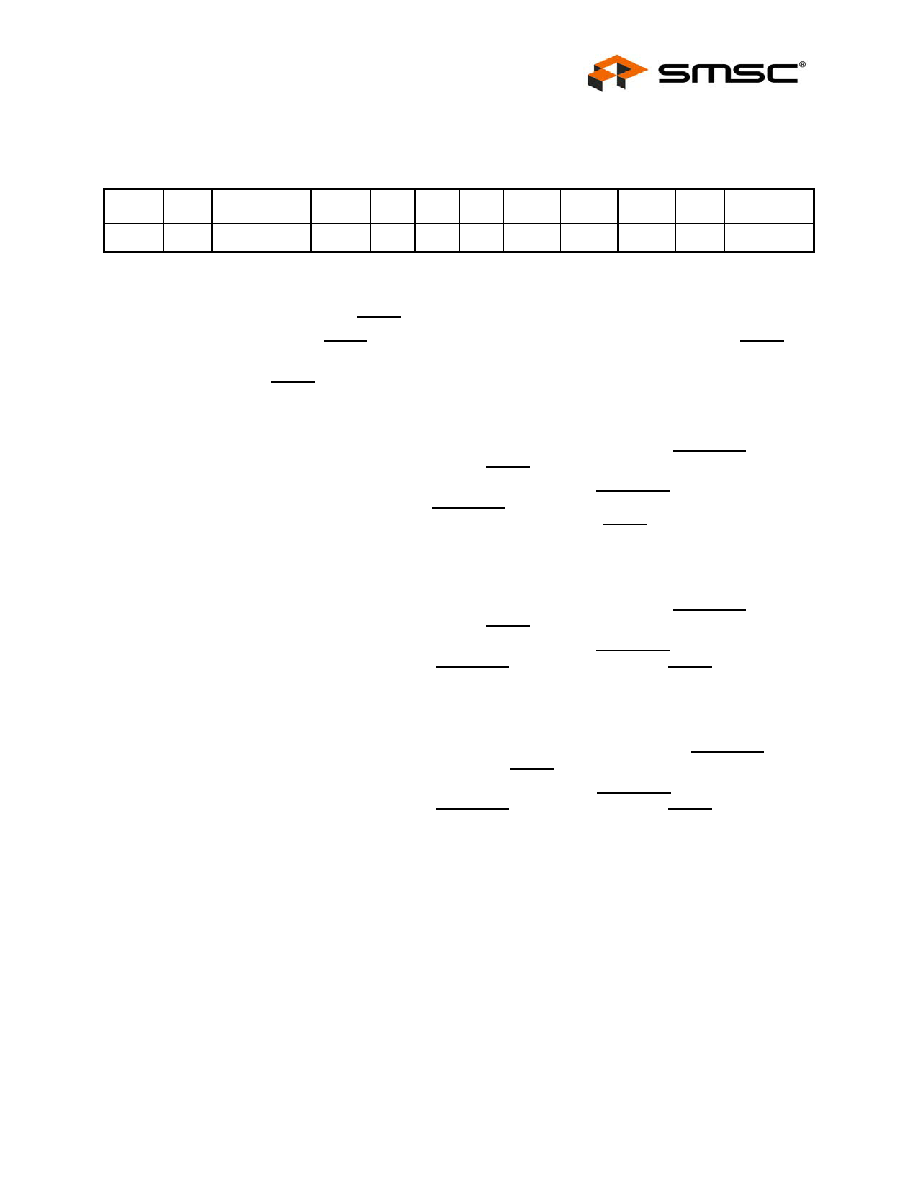

Table 6.15 Configuration Register

ADDR

R/W

REGISTER

B7

B6

B5

B4

B3

B2

B1

B0

DEFAULT

20h

R/W

Configuration

MASK

-

SYS3

SYS2

SYS1

APD

00h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EMC2103-2-AP-TR | |

| EMCL12C2J-35.000MTR | CRYSTAL OSCILLATOR, CLOCK, 35 MHz, LVPECL OUTPUT |

| EMCL12C2J-40.000M | CRYSTAL OSCILLATOR, CLOCK, 40 MHz, LVPECL OUTPUT |

| EMCL12D2H-30.000MTR | CRYSTAL OSCILLATOR, CLOCK, 30 MHz, LVPECL OUTPUT |

| EMCL12D2H-40.000MTR | CRYSTAL OSCILLATOR, CLOCK, 40 MHz, LVPECL OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EMC2103-2 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:Analog and Interface Product Selector Guide |

| EMC2103-2-AP | 制造商:SMSC 制造商全稱:SMSC 功能描述:RPM-Based Fan Controller with HW Thermal Shutdown |

| EMC2103-2-AP-TR | 功能描述:板上安裝溫度傳感器 Closed Loop RPM RPM Fan Ctrl 3Remote RoHS:否 制造商:Omron Electronics 輸出類型:Digital 配置: 準(zhǔn)確性:+/- 1.5 C, +/- 3 C 溫度閾值: 數(shù)字輸出 - 總線接口:2-Wire, I2C, SMBus 電源電壓-最大:5.5 V 電源電壓-最小:4.5 V 最大工作溫度:+ 50 C 最小工作溫度:0 C 關(guān)閉: 安裝風(fēng)格: 封裝 / 箱體: 設(shè)備功能:Temperature and Humidity Sensor |

| EMC2103-3-KP | 制造商:SMSC 制造商全稱:SMSC 功能描述:RPM-Based Fan Controller with HW Thermal Shutdown |

| EMC2103-4 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:Analog and Interface Product Selector Guide |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。