- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384295 > EM48AM3284LBA (Electronic Theatre Controls, Inc.) 512Mb (4M】4Bank】32) Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | EM48AM3284LBA |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 512Mb (4M】4Bank】32) Synchronous DRAM |

| 中文描述: | 的512Mb(4分】4Bank】32)同步DRAM |

| 文件頁數(shù): | 8/17頁 |

| 文件大小: | 231K |

| 代理商: | EM48AM3284LBA |

eorex

EM48AM3284LBA

Jul. 2006

www.eorex.com

8/17

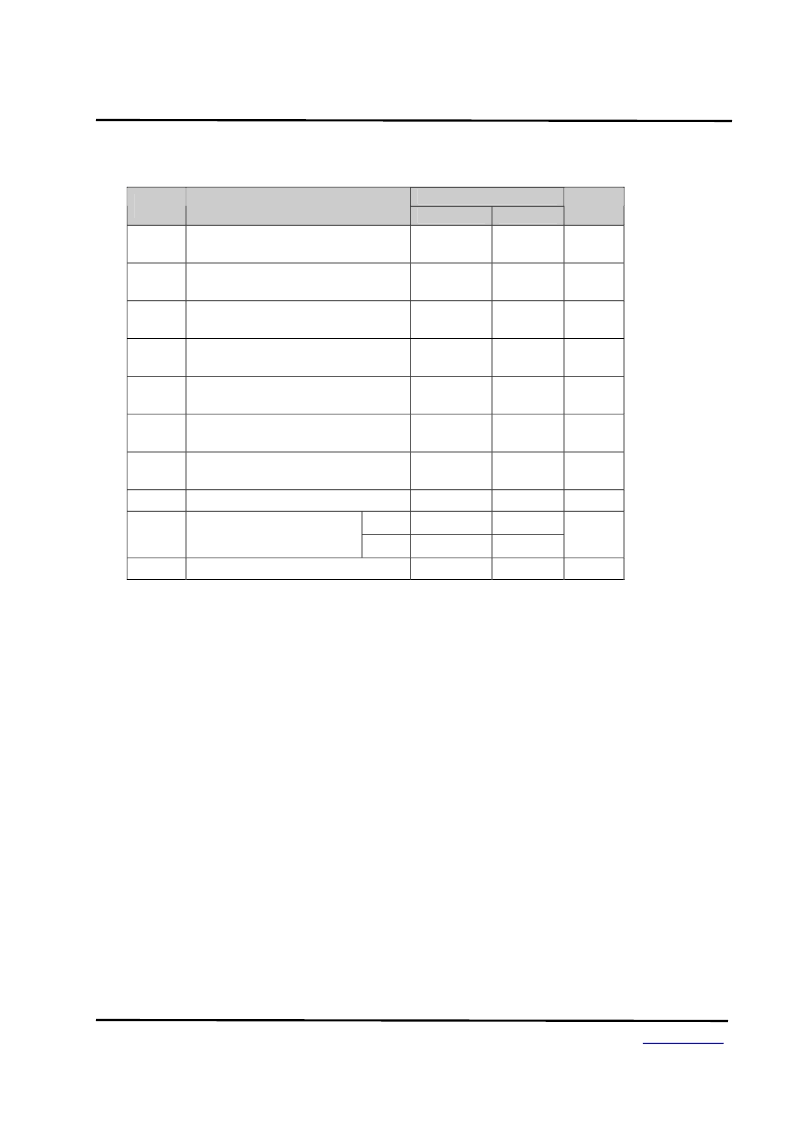

AC Operating Test Characteristics (Continued)

(V

DD

=1.8V

±

0.1V, T

A

=0°C ~70°C)

-75

Symbol

Parameter

Min.

Max.

Units

t

RC

ACTIVE to ACTIVE Command

Period

(Note 6)

ACTIVE to PRECHARGE

Command Period

(Note 6)

PRECHARGE to ACTIVE

Command Period

(Note 6)

ACTIVE to READ/WRITE Delay

Time

(Note 6)

ACTIVE(one) to ACTIVE(another)

Command

(Note 6)

READ/WRITE Command to

READ/WRITE Command

90

t

RAS

60

120k

ns

t

RP

22.5

ns

t

RCD

30

ns

t

RRD

2

CLK

t

CCD

1

CLK

t

DPL

Date-in to PRECHARGE

Command

Date-in to BURST Stop Command

Data-out to High

Impedance from

PRECHARGE Command

Refresh Time (8,192 cycle)

* All voltages referenced to V

SS

.

Note 6:

These parameters account for the number of clock cycles and depend on the operating frequency

of the clock, as follows:

The number of clock cycles = Specified value of timing/clock period (Count Fractions as a whole

number)

2

CLK

t

BDL

1

CLK

CL=3

2CK+22.5

t

ROH

CL=2

2CK+22.5

ns

t

REF

64

ms

Recommended Power On and Initialization

The following power on and initialization sequence guarantees the device is preconditioned to each user’s

specific needs. (Like a conventional DRAM) During power on, all V

DD

and V

DDQ

pins must be built up

simultaneously to the specified voltage when the input signals are held in the “NOP” state. The power on

voltage must not exceed V

DD

+0.3V on any of the input pins or V

DD

supplies. (CLK signal started at same

time)

After power on, an initial pause of 200 μs is required followed by a precharge of all banks using the

precharge command.

To prevent data contention on the DQ bus during power on, it is required that the DQM and CKE pins be

held high during the initial pause period. Once all banks have been precharged, the Mode Register Set

Command must be issued to initialize the Mode Register. A minimum of eight Auto Refresh cycles (CBR)

are also required, and these may be done before or after programming the Mode Register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EM48AM3284LBA-75F | 512Mb (4M】4Bank】32) Synchronous DRAM |

| EM48AM3284LBA-75FE | 512Mb (4M】4Bank】32) Synchronous DRAM |

| EM512D16 | 512K x 16 bit Ultra-Low Power Asynchronous Static RAM |

| EM6011 | ELECTRET CONDENSER MICROPHONE |

| EM6011-BC | ELECTRET CONDENSER MICROPHONE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EM48AM3284LBA_09 | 制造商:EOREX 制造商全稱:EOREX 功能描述:512Mb (4M×4Bank×32) Synchronous DRAM |

| EM48AM3284LBA-6FH | 制造商:EOREX 制造商全稱:EOREX 功能描述:512Mb (4M×4Bank×32) Synchronous DRAM |

| EM48AM3284LBA-6FS | 制造商:EOREX 制造商全稱:EOREX 功能描述:512Mb (4M×4Bank×32) Synchronous DRAM |

| EM48AM3284LBA-75F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512Mb (4M×4Bank×32) Synchronous DRAM |

| EM48AM3284LBA-75FE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512Mb (4M×4Bank×32) Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。