- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9748 > DS32512+ (Maxim Integrated Products)IC LIU DS3/E3/STS-1 484-BGA PDF資料下載

參數(shù)資料

| 型號(hào): | DS32512+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 129/130頁(yè) |

| 文件大小: | 0K |

| 描述: | IC LIU DS3/E3/STS-1 484-BGA |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 30 |

| 類型: | 線路接口裝置(LIU) |

| 規(guī)程: | DS3 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 484-BGA |

| 供應(yīng)商設(shè)備封裝: | 484-BGA(23x23) |

| 包裝: | 管件 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)當(dāng)前第129頁(yè)第130頁(yè)

DS32506/DS32508/DS32512

98 of 130

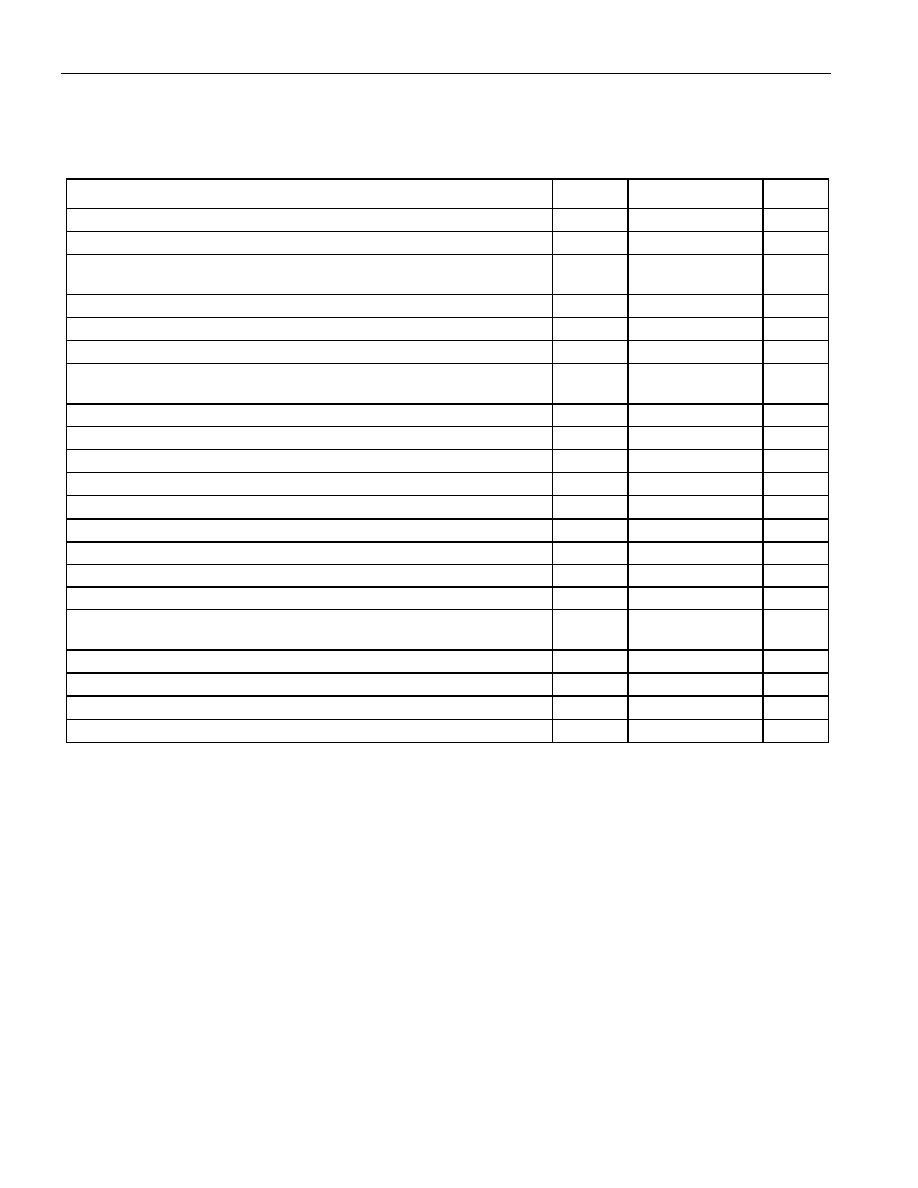

Table 11-8. Parallel CPU Interface Timing

(VDD18 = 1.8V

±5%, VDD33 = 3.3V ±5%, AVDD = 1.8V ±5%, TA = -40°C to +85°C.)

PARAMETER

SYMBOL MIN TYP MAX

UNITS

t1

0

ns

t2

0

ns

Handshake

t3a

65

ns

Delay Time from RDY or ACK Active to D[15:0] Valid

t3b

20

ns

t4

0

ns

t5

2

ns

Handshake

t6a

65

ns

Wait Time from RDY or ACK Active to Latch D[15:0]

t6b

20

ns

t7

10

ns

t8

2

ns

t9a

5

ns

t9b

20

ns

t10

75

ns

Muxed Address Valid to ALE Inactive (Note 4)

t11

10

ns

Muxed Address Hold Time from ALE Inactive (Note 4)

t12

10

ns

ALE Pulse Width (Note 4)

t13

20

ns

Setup Time for ALE High or Muxed Address Valid to CS Active

(Notes 4, 5, 6)

t14

0

ns

Delay from CS Inactive to D[15:0] Disable

t15

15

ns

Delay from CS Active to RDY/ACK Enable

t16

15

ns

t17

2

ns

Delay from CS Inactive to RDY/ACK Disable

t18

15

ns

Note 1:

D[15:0] loaded with 50pF when tested as outputs.

Note 2:

If a gapped clock is applied on TCLK and local loopback is enabled, read cycle time must be extended by the length of the largest

TCLK gap.

Note 3:

Not tested during production test.

Note 4:

In nonmultiplexed bus applications (Figure 11-3 to Figure 11-6), ALE should be wired high. In multiplexed bus applications (Figure

11-7 to Figure 11-10), A[10:0] should be wired to D[15:0] and the falling edge of ALE latches the address.

Note 5:

t14 starts at the occurrence of the rising edge of ALE or A[10:0] valid whichever occurs later.

Note 6:

In order to avoid bus contention, during a read cycle A[10:0] should be disabled prior to RD or DS being active.

Note 7:

RDY/ACK may be disabled (t18) before going inactive (t17).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-26W-IU-F2 | CONVERTER MOD DC/DC 5.5V 200W |

| M83723/71W1020Y | CONN RCPT 2POS WALL MT W/SCKT |

| DS3154+ | IC LIU DS3/E3/STS1 QUAD 144CSBGA |

| MAX1228ACEP+T | IC ADC 12BIT 300KSPS 20-QSOP |

| VE-211-IW-B1 | CONVERTER MOD DC/DC 12V 100W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS32512+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS32512A2 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS32512DK | 功能描述:網(wǎng)絡(luò)開(kāi)發(fā)工具 DS32512 Dev Kit RoHS:否 制造商:Rabbit Semiconductor 產(chǎn)品:Development Kits 類型:Ethernet to Wi-Fi Bridges 工具用于評(píng)估:RCM6600W 數(shù)據(jù)速率:20 Mbps, 40 Mbps 接口類型:802.11 b/g, Ethernet 工作電源電壓:3.3 V |

| DS32512N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS32512N# | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12-Port DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。