- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166631 > BU-65527C3-300 (DATA DEVICE CORP) 3 CHANNEL(S), MIL-STD-1553 CONTROLLER, XMA PDF資料下載

參數(shù)資料

| 型號: | BU-65527C3-300 |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 3 CHANNEL(S), MIL-STD-1553 CONTROLLER, XMA |

| 文件頁數(shù): | 27/32頁 |

| 文件大?。?/td> | 2094K |

| 代理商: | BU-65527C3-300 |

4

Data Device Corporation

www.ddc-web.com

BU-65528 and BU-65527

F1 web-10/02-0

the bus interface to be VME and adds hardware and software

features which are tailored to test and instrumentation systems.

The key architectural features of the BU-65528/27 over a gener-

ic VME board which make it compliant to VXI are in register def-

inition, memory map of the VME short address space, the map-

ping of device memory into VME standard and extended address

spaces, and the use of the P2 connector.

The VXIbus specification allocates a block of 64 bytes for regis-

ters on each card within the VME Short (A16) address space.

VXI further defines the content and function of the first four 16-

bit registers (ID/Logical address, device type, status/control, and

offset). The remaining 28 words are device dependent.

The entire P1 connector and the middle row of the P2 connector

are defined within the VXIbus standard to be the same as the

definition in the VMEbus standard. The outer rows on the P2 con-

nector, which are user defined in the VMEbus standard, have

specific assignments within the VXIbus standard.

The BU-65528/27 implements the mapping and functionality of

the required VXI registers. This includes the definition of the

memory offset register which is used to program the base

address of the BU-65528/27's buffer memory within the VME

standard (A24) or VME extended (A32) address space.

The BU-65528/27 does not make use of any VXI-defined pins on

the outer rows of the P2 connector and implements the remain-

ing P2 signals and all P1 signals as per the VMEbus specifica-

tion. It should be noted that the militarized BU-65527X card uses

the outer rows of the P2 connector for the 1553 bus signals, RT

address, and register base address. The BU-65527X's device

dependent use of the P2 connector, while fully compliant with the

VMEbus specification, makes it non-compliant with VXIbus stan-

dard.

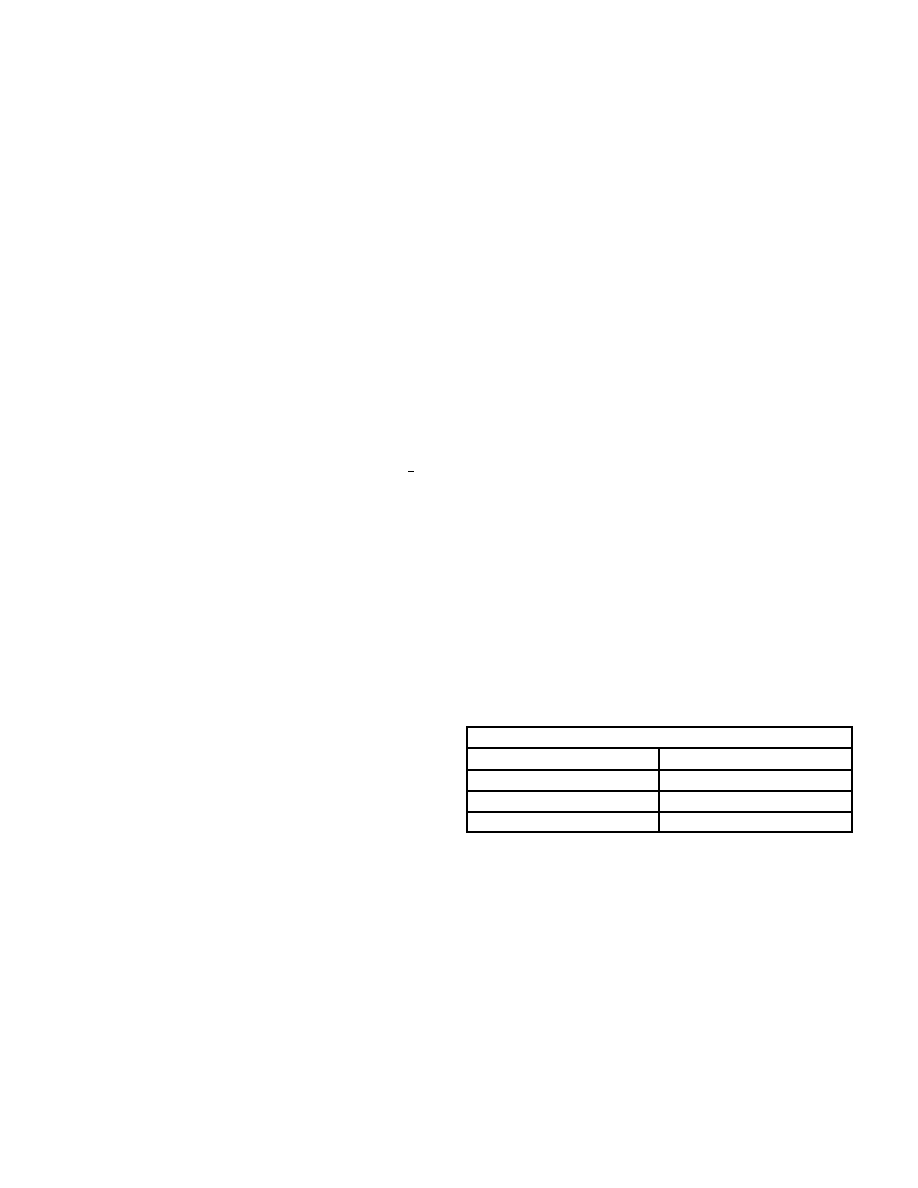

ADDRESS MODIFIERS

The address modifiers are programmed as listed in TABLE 2.

Register provides the current state of the interrupt conditions.

The Interrupt Status Register may be updated in two ways. In

the standard interrupt handling mode, a particular bit in the

Interrupt Status Register will be updated only if the condition

exists and the corresponding bit in the Interrupt Mask Register is

enabled. In the enhanced interrupt handling mode, a particular

bit in the Interrupt Status Register will be updated if the condition

exists regardless of the contents of the corresponding Interrupt

Mask Register bit. In any case, the respective Interrupt Mask

Register bit enables an interrupt for a particular condition.

The BU-65528/27 provides maskable interrupts and 15-bit

Interrupt Status Register for End Of Message(EOM), end-of-BC

message list, erroneous messages, Status Set (BC mode), Time

Tag Register Rollover, RT Address Parity Error conditions, BC

retry, data stack rollover, command stack rollover, transmitter

watchdog timeout, or RAM parity error. The Interrupt Status

Register allows the host processor to determine the cause of all

interrupts by means of a single READ operation.

INTERNAL COMMAND ILLEGALIZATION

The BU-65528/27 offers the option to illegalize commands in RT

mode. The illegalization architecture allows for any subset of the

4096 possible combinations of broadcast/own address,

bit,

subaddress, and word count/mode code to be illegalized. The

BU-65528/27 illegalization scheme is under software control of

the host processor. As a result, it is inherently self-testable.

INTERNAL TIME TAG

The BU-65528/27 includes an internal read/writable Time Tag

Register. This register is a CPU read/writable 16-bit counter with

a programmable resolution of either 2, 4, 8, 16, 32, or 64

s per

LSB. Another option allows the Time Tag Register to be incre-

mented under software control. This supports self-test for the

Time Tag Register.

For each message processed, the value of the Time Tag register

is loaded into the second location of the respective descriptor

stack entry (“TIME TAG WORD”) for both BC and RT modes.

Additional options are provided to clear the Time Tag Register

following a Synchronize (without data) mode command or load

the Time Tag Register following a Synchronize (with data) mode

command. Another option enables an interrupt request and a bit

in the Interrupt Status Register to be set when the Time Tag

Register rolls over from FFFF to 0000(hex). Assuming the Time

Tag Register is not loaded or reset, this will occur at approxi-

mately 4-second time intervals, for 64

s/LSB resolution, down

to 131 ms intervals, for 2

s/LSB resolution.

Another programmable option for RT mode is for the Service

Request Status Word bit to be automatically cleared following the

BU-65528/27's response to a Transmit Vector Word mode com-

mand.

VME AND VXI

The BU-65528/27 is compliant to both VMEbus and VXIbus.

VXIbus,

also

referred

to

as

VMEbus

Extensions

for

Instrumentation, is a functional superset of VMEbus. VXI defines

R

/

T

TABLE 2. ADDRESS MODIFIERS

ADDRESS

MODIFIERS

A16

29, 2D

A24

3D, 3E, 39, 3A

A32

0D, 0E, 09, 0A

ADDRESSING, INTERNAL REGISTERS, MEMORY

MANAGEMENT, AND INTERRUPTS

ADDRESSING THE BU-65528/27

The software interface of the host processor to a single 1553

channel consists of 22 internal operational registers for normal

operation, an additional 8 test registers, plus 12K x 16 of shared

memory.

The internal registers occupy 64 bytes in the VME/VXI A16

address space while the 12K x 16 of shared RAM resides in

either the A24 or A32 address space. The A24 and A32 support

is software programmable using the I/O address selector pins on

the P2 connector (BU-65527MX is hardwired for A24 address

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-65743F3-300 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65863F3-310 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65743F3-200 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65863F3-220 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-65843B3-E02 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, PBGA324 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU6554GVW | 制造商:ROHM 制造商全稱:Rohm 功能描述:Home Electronics and Security Devices IC |

| BU-65-6 | 功能描述:測試電夾 ALLIGATOR CLIP BLU RoHS:否 制造商:Pomona Electronics 類型:Minigrabber clip 顏色:Black |

| BU-656-0 | 功能描述:測試電夾 Black Safety Alligat RoHS:否 制造商:Pomona Electronics 類型:Minigrabber clip 顏色:Black |

| BU65612P0-100 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| BU65612P0-110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。