- 您現(xiàn)在的位置:買賣IC網 > PDF目錄375384 > AX88796BLF (ASIX Electronics Corporation) IC,MC14411P PDF資料下載

參數(shù)資料

| 型號: | AX88796BLF |

| 廠商: | ASIX Electronics Corporation |

| 英文描述: | IC,MC14411P |

| 中文描述: | 低引腳數(shù)的非PCI 16位產品10/100M自適應快速以太網控制器 |

| 文件頁數(shù): | 9/82頁 |

| 文件大小: | 519K |

| 代理商: | AX88796BLF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

ASIX ELECTRONICS CORPORATION

9

AX88796BLF / AX88796BLI

3.0 Memory and CSR Mapping

1.

EEPROM Memory Mapping

2.

CSR Mapping

3.

Local Memory Mapping

3.1 EEPROM Memory Mapping

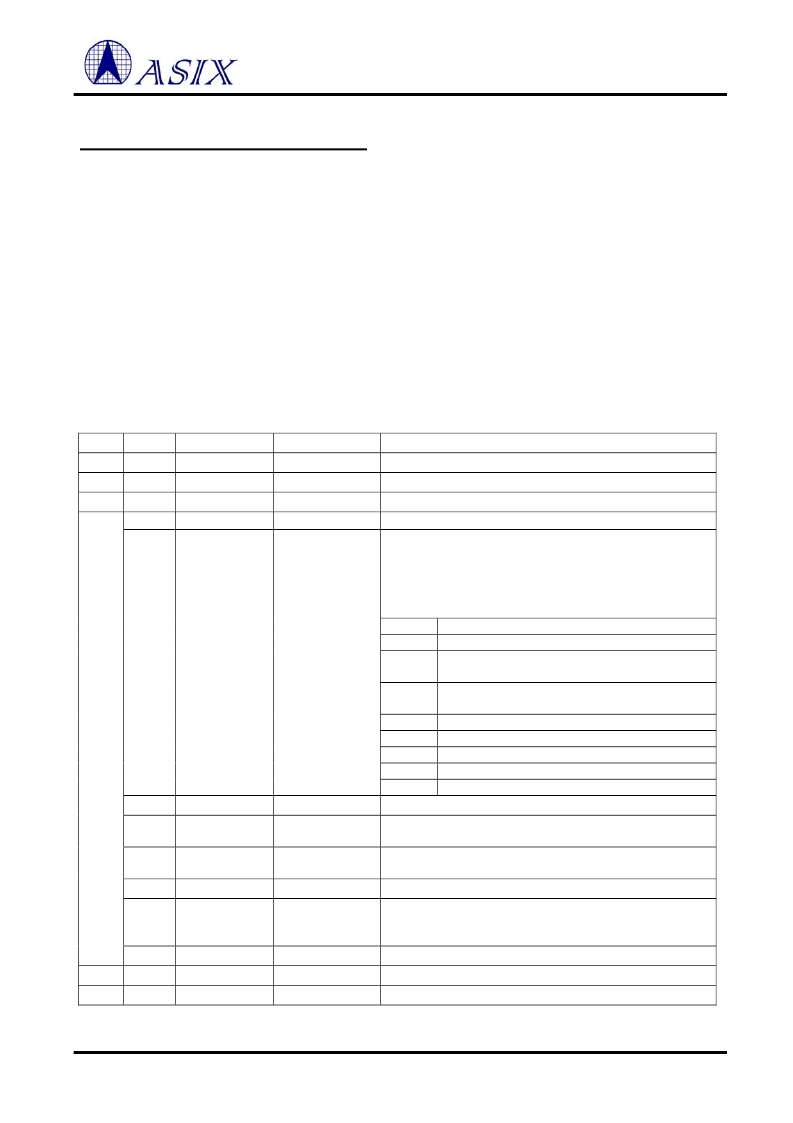

EEPROM interface can access via CSR offset 14h SMI/EEPROM registers when auto load operation completed.

The content of EEPROM data will be auto-loaded to internal memory from 0000h to 001Fh and from 0400h to

040Fh automatically when hardware reset. It is similar to NE2000 PROM store Ethernet address. The real MAC

address must configured by PAR0 ~ PAR5 (CR page1 offset1 ~ offset6). The auto-loader only write to internal

SRAM not write to PAR0 ~ PAR5. An example as below, if the desired Ethernet physical address is

10-32-54-76-98-BA

It is a programmed EEPROM if auto-load value is 5AA5h from EEPROM address 0h. After hardware reset the

EEPROM loader will read first word and check pattern 5AA5h. If the first word value not equal to 5AA5h then the

EEPROM loader proclaimed that no external EEPROM or external EEPROM is a non-programmed EEPROM.

Addr

Bits

D[15:8]

D[7:0]

5h

[15:0]

BAh

98h

MAC address 6

th

, 5

th

4h

[15:0]

76h

54h

MAC address 4

th

, 3

rd

3h

[15:0]

32h

10h

MAC address 2

nd

, 1

st

(multicast bit is 1

st

of bit_0)

[15:11]

No define

Always zero

Configure internal PHY in different ways, such as 10BASE_T

half-duplex mode. If EEPROM auto loader not found 5AA5h

pattern in first word then internal PHY will be not been manual

configuration. (Default is Auto-negotiation enable with all

capabilities)

Description

[10:8]

000

001

Function

Auto-negotiation enable with all capabilities

Auto-negotiation with 100BASE-TX FDX / HDX

ability

Auto-negotiation with 10BASE-T FDX / HDX

ability

Reserved

Manual selection of 100BASE-TX FDX

Manual selection of 100BASE-TX HDX

Manual selection of 10BASE-T FDX

Manual selection of 10BASE-T HDX

Always zero

IRQ_TYPE_EEP This bit will logic OR with BTCR (15h) bit-5 and will been

clear when host write BTCR. (Offset 15h)

IRQ_POL_EEP

This bit will logic OR with BTCR (15h) bit-4 and will been

clear when host write BTCR. (Offset 15h)

No define

Always zero

NE2000_PROM When set, AX88796B internal memory map of 1Ch ~ 1Fh will

be configured to 57h. An ASCII code “W”. Otherwise

configured to 42h. An ASCII code “B”.

No define

Always zero

06h

Indicates the total of word counts for auto loading

A5h

Programmed pattern

010

011

100

101

110

111

[10:8]

PHY_CONFIG

[7:6]

[5]

No define

[4]

[3]

[2]

2h

[1:0]

[15:0]

[15:0]

1h

0h

00h

5Ah

Tab - 6 EEPROM data format example

相關PDF資料 |

PDF描述 |

|---|---|

| AX88796BLI | Low-pin-count Non-PCI 8/16-bit 10/100M Fast Ethernet Controller |

| AX88872P | 10/100BASE Dual Speed “Swipeater” Controller |

| AX9902MS | 2N and 2P-Channel Enhancement Mode Power MOSFET |

| AX9902MSA | 2N and 2P-Channel Enhancement Mode Power MOSFET |

| AXC-051 | ACTIVE FILTER FOR RIPPLE ATTENUATION 5A |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AX88796BLI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:High-Performance Non-PCI Single-Chip 8/16 bit 10/100M Fast Ethernet Controller |

| AX88796C | 制造商:ASIX 制造商全稱:ASIX 功能描述:Low-Power SPI or Non-PCI Ethernet Controller |

| AX88796CLF | 制造商:ASIX Electronics Corporation 功能描述: |

| AX88796L | 制造商:ASIX 制造商全稱:ASIX 功能描述:3-in-1 Local Bus Fast Ethernet Controller |

| AX88796LF | 制造商:ASIX 功能描述:10/100 MAC |

發(fā)布緊急采購,3分鐘左右您將得到回復。