- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374046 > ADV7171 (Analog Devices, Inc.) Digital PAL/NTSC Video Encoder(數(shù)字PAL/NTSC視頻編碼器) PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7171 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Digital PAL/NTSC Video Encoder(數(shù)字PAL/NTSC視頻編碼器) |

| 中文描述: | 數(shù)碼PAL / NTSC視頻編碼器(數(shù)字PAL / NTSC制式視頻編碼器) |

| 文件頁數(shù): | 28/55頁 |

| 文件大?。?/td> | 580K |

| 代理商: | ADV7171 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

ADV7170/ADV7171

–28–

REV. 0

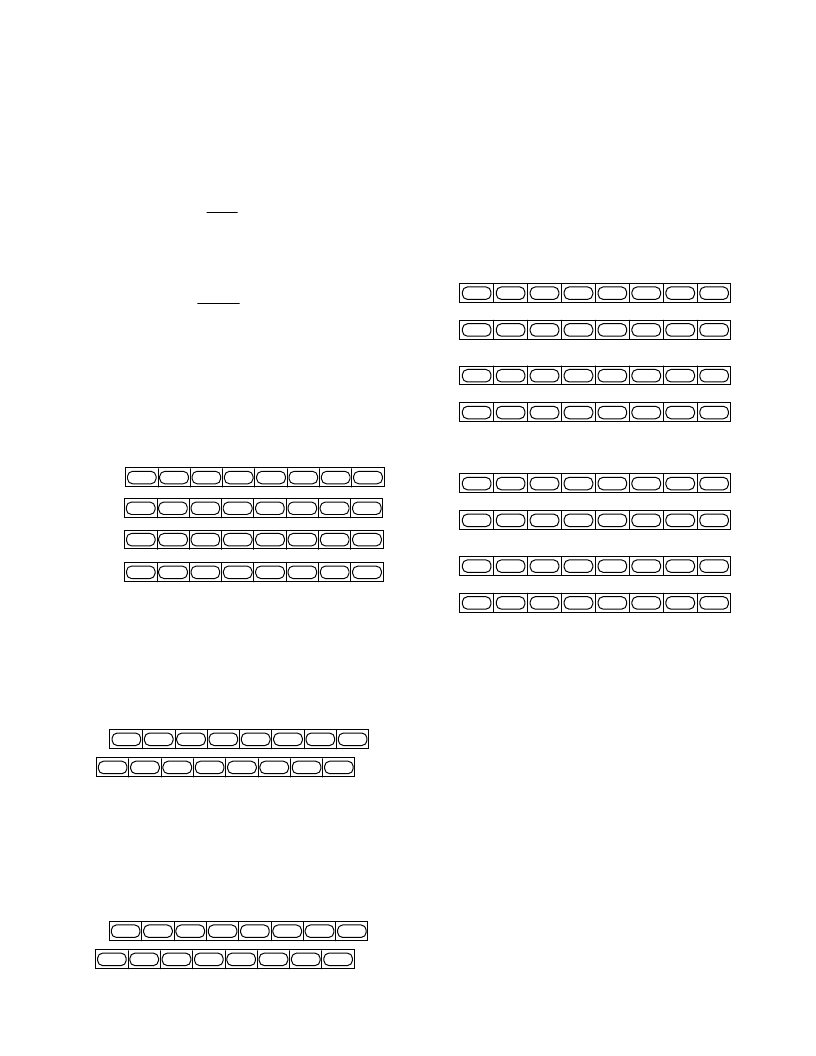

SUBCARRIER FREQUENCY REGISTER 3–0

(FSC3–FSC0)

(Address [SR4–SR0] = 09H–02H)

These 8-bit-wide registers are used to set up the subcarrier

frequency. The value of these registers is calculated by using the

following equation:

Subcarrier Frequency Register

=

2

32

–1

F

CLK

×

F

SCF

i.e.: NTSC Mode,

F

CLK

= 27 MHz,

F

SCF

= 3.5795454 MHz

Subcarrier Frequency Value

=

2

32

–1

27

×

10

6

×

3.5795454

×

10

6

= 21F07C16

HEX

Figure 45 shows how the frequency is set up by the four registers.

SUBCARRIER PHASE REGISTER (FP7–FP0)

(Address [SR4–SR0] = 0DH)

This 8-bit-wide register is used to set up the subcarrier phase.

Each bit represents 1.41

°

. For normal operation this register is

set to 00Hex.

SUBCARRIER

FREQUENCY

REG 3

SUBCARRIER

FREQUENCY

REG 2

SUBCARRIER

FREQUENCY

REG 1

SUBCARRIER

FREQUENCY

REG 0

FSC30

FSC29

FSC27

FSC25

FSC28

FSC24

FSC31

FSC26

FSC22

FSC21

FSC19

FSC17

FSC20

FSC16

FSC23

FSC18

FSC14

FSC13

FSC11

FSC9

FSC12

FSC8

FSC15

FSC10

FSC6

FSC5

FSC3

FSC1

FSC4

FSC0

FSC7

FSC2

Figure 45. Subcarrier Frequency Register

CLOSED CAPTIONING EVEN FIELD

DATA REGISTER 1–0 (CED15–CED00)

(Address [SR4–SR0] = 0E–0FH)

These 8-bit-wide registers are used to set up the closed captioning

extended data bytes on even fields. Figure 46 shows how the

high and low bytes are set up in the registers.

BYTE 1

BYTE 0

CED6

CED5

CED3

CED1

CED4

CED2

CED0

CED7

CED14

CED13

CED11

CED9

CED12

CED10

CED8

CED15

Figure 46. Closed Captioning Extended Data Register

CLOSED CAPTIONING ODD FIELD

DATA REGISTER 1–0 (CCD15–CCD00)

(Subaddress [SR4–SR0] = 10–11H)

These 8-bit-wide registers are used to set up the closed

captioning data bytes on odd fields. Figure 47 shows how the

high and low bytes are set up in the registers.

BYTE 1

BYTE 0

CCD6

CCD5

CCD3

CCD1

CCD4

CCD2

CCD0

CCD7

CCD14

CCD13

CCD11

CCD9

CCD12

CCD10

CCD8

CCD15

Figure 47. Closed Captioning Data Register

NTSC PEDESTAL/PAL TELETEXT CONTROL

REGISTERS 3–0 (PCE15–0, PCO15–0)/(TXE15–0, TXO15–0)

(Subaddress [SR4–SR0] = 12–15H)

These 8-bit-wide registers are used to enable the NTSC pedes-

tal/PAL Teletext on a line-by-line basis in the vertical blanking

interval for both odd and even fields. Figures 48 and 49 show

the four control registers. A Logic “1” in any of the bits of these

registers has the effect of turning the Pedestal OFF on the

equivalent line when used in NTSC. A Logic “1” in any of the

bits of these registers has the effect of turning Teletext ON on

the equivalent line when used in PAL.

FIELD 1/3

PCO6

PCO5

PCO3

PCO1

PCO4

PCO2

PCO0

PCO7

LINE 17 LINE 16 LINE 15 LINE 14 LINE 13 LINE 12 LINE 11 LINE 10

PCO14

PCO13

PCO11

PCO9

PCO12

PCO10

PCO8

PCO15

LINE 25 LINE 24 LINE 23 LINE 22 LINE 21 LINE 20 LINE 19 LINE 18

FIELD 1/3

FIELD 2/4

PCE6

PCE5

PCE3

PCE1

PCE4

PCE2

PCE0

PCE7

LINE 17 LINE 16 LINE 15 LINE 14 LINE 13 LINE 12 LINE 11 LINE 10

PCE14

PCE13

PCE11

PCE9

PCE12

PCE10

PCE8

PCE15

LINE 25 LINE 24 LINE 23 LINE 22 LINE 21 LINE 20 LINE 19 LINE 18

FIELD 2/4

Figure 48. Pedestal Control Registers

FIELD 1/3

FIELD 1/3

FIELD 2/4

FIELD 2/4

TXO6

TXO5

TXO3

TXO1

TXO4

TXO2

TXO0

TXO7

LINE 14 LINE 13 LINE 12 LINE 11 LINE 10 LINE 9

LINE 8 LINE 7

TXO14

TXO13

TXO11

TXO9

TXO12

TXO10

TXO8

TXO15

LINE 22 LINE 21 LINE 20 LINE 19 LINE 18 LINE 17 LINE 16 LINE 15

TXE6

TXE5

TXE3

TXE1

TXE4

TXE2

TXE0

TXE7

TXE14

TXE13

TXE11

TXE9

TXE12

TXE10

TXE8

TXE15

LINE 14 LINE 13 LINE 12 LINE 11 LINE 10 LINE 9

LINE 8

LINE 7

LINE 22 LINE 21 LINE 20 LINE 19 LINE 18 LINE 17 LINE 16 LINE 15

Figure 49. Teletext Control Registers

TELETEXT CONTROL REGISTER TC07 (TC07–TC00)

(Address [SR4–SR0] = 19H)

Teletext Control Register is an 8-bit-wide register. See Figure 50.

TTXREQ Rising Edge Control (TC07–TC04)

These bits control the position of the rising edge of TTXREQ.

It can be programmed from zero CLOCK cycles to a max of 15

CLOCK cycles. See Figure 59.

TTXREQ Falling Edge Control (TC03–TC00)

These bits control the position of the falling edge of TTXREQ.

It can be programmed from zero CLOCK cycles to a max of 15

CLOCK cycles. This controls the active window for Teletext

data. Increasing this value reduces the amount of Teletext bits

below the default of 360. If Bits TC03-TC00 are 00Hex when

bits TC07–TC04 are changed, the falling edge of TTREQ will

track that of the rising edge (i.e., the time between the falling

and rising edge remains constant). See Figure 59.

CGMS_WSS REGISTER 0 C/W0 (C/W07–C/W00)

(Address [SR4–SR0] = 16H)

CGMS_WSS Register 0 is an 8-bit-wide register. Figure 51

shows the operations under the control of this register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7173KST | Digital PAL/NTSC Video Encoder with Six DACs 10 Bits, Color Control and Enhanced Power Management |

| ADV7172KST | Digital PAL/NTSC Video Encoder with Six DACs 10 Bits, Color Control and Enhanced Power Management |

| ADV7172 | Digital PAL/NTSC Video Encoder with Six DACs 10 Bits, Color Control and Enhanced Power Management |

| ADV7173 | Digital PAL/NTSC Video Encoder with Six DACs 10 Bits, Color Control and Enhanced Power Management |

| ADV7173* | Digital PAL/NTSC Video Encoder with Six DACs (10 Bits). Color Control and Enhanced Power Management |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7171KS | 制造商:Analog Devices 功能描述:Video Encoder 4DAC 10-Bit 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:ADVANCED NTSC/PAL ENCODER I.C. - Bulk 制造商:Analog Devices 功能描述:IC VIDEO ENCODER 制造商:Panasonic Industrial Company 功能描述:IC |

| ADV7171KS-REEL | 制造商:Analog Devices 功能描述:Video Encoder 4DAC 10-Bit 44-Pin MQFP T/R 制造商:Rochester Electronics LLC 功能描述:ADVANCED NTSC/PAL ENCODER I.C. - Tape and Reel |

| ADV7171KSU | 制造商:Analog Devices 功能描述:Video Encoder 4DAC 10-Bit 44-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:ADVANCED NTSC/PAL ENCODER - Bulk 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7171KSU-REEL | 制造商:Analog Devices 功能描述:Video Encoder 4DAC 10-Bit 44-Pin TQFP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。