- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374037 > ADSP-21XX1111 (Analog Devices, Inc.) ADSP-2100 Family DSP Microcomputers PDF資料下載

參數(shù)資料

| 型號: | ADSP-21XX1111 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | ADSP-2100 Family DSP Microcomputers |

| 中文描述: | 的ADSP - 2100系列DSP的微機 |

| 文件頁數(shù): | 5/32頁 |

| 文件大?。?/td> | 231K |

| 代理商: | ADSP-21XX1111 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

ADSP-21mod870

–5–

REV. 0

Memory Interface Pins

The ADSP-21mod870 processor can be used in one of two

modes: Full Memory Mode, which allows BDMA operation

with full external overlay memory and I/O capability, or Host

Mode, which allows IDMA operation with limited external

addressing capabilities. The operating mode is determined by

the state of the Mode C pin during RESET and cannot be

changed while the processor is running.

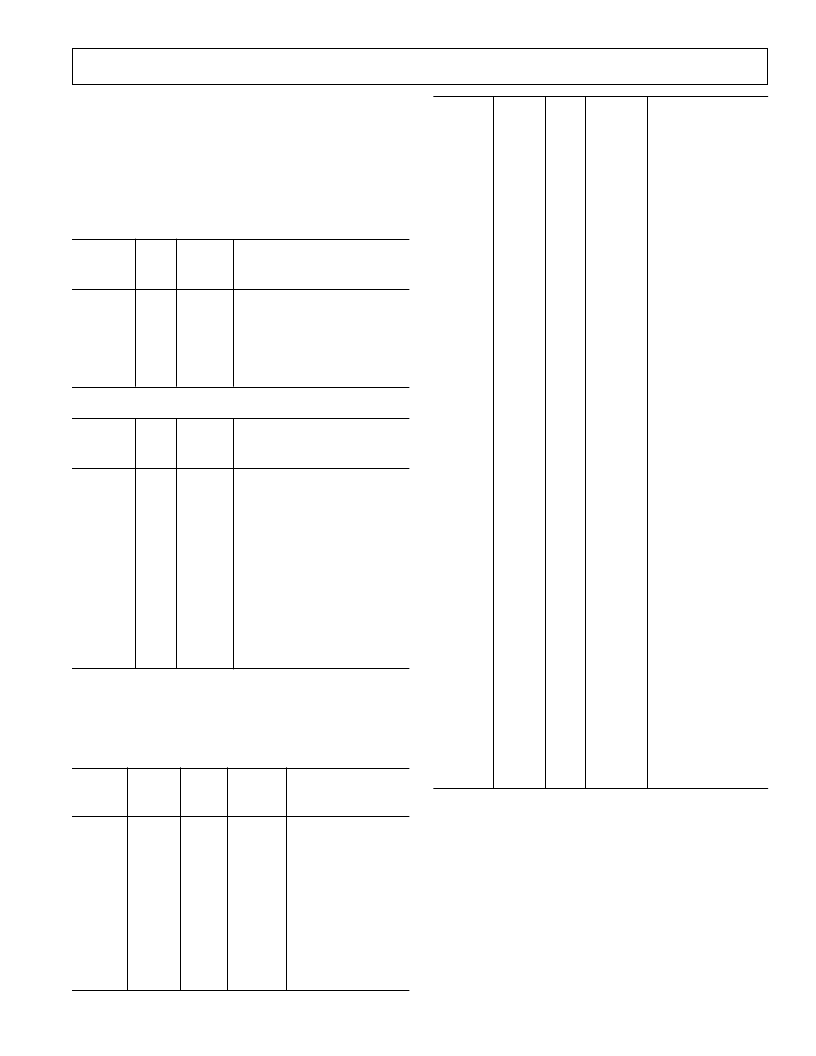

Full Memory Mode Pins (Mode C = 0)

#

of

Pins

Input/

Output

Pin Name

Function

A13:0

14

O

Address Output Pins for Pro-

gram, Data, Byte and I/O Spaces

Data I/O Pins for Program,

Data, Byte and I/O Spaces

(8 MSBs Are Also Used as

Byte Memory Addresses)

D23:0

24

I/O

Host Mode Pins (Mode C = 1)

#

of

Pins

Input/

Output

Pin Name

Function

IAD15:0

A0

16

1

I/O

O

IDMA Port Address/Data Bus

Address Pin for External I/O,

Program, Data, or Byte Access

Data I/O Pins for Program,

Data Byte and I/O Spaces

IDMA Write Enable

IDMA Read Enable

IDMA Address Latch Pin

IDMA Select

IDMA Port Acknowledge

Configurable in Mode D; Open

Drain

D23:8

16

I/O

IWR

IRD

IAL

IS

IACK

1

1

1

1

1

I

I

I

I

O

In Host Mode, external peripheral addresses can be decoded using the A0,

CMS

,

PMS

,

DMS

and

IOMS

signals.

Terminating Unused Pin

The following table shows the recommendations for terminating

unused pins.

Pin Terminations

I/O

3-State

(Z)

Hi-Z*

Caused

By

Pin

Name

Reset

State

Unused

Configuration

XTAL

CLKOUT

A13:1 or

IAD12:0

A0

D23:8

D7 or

IWR

D6 or

IRD

D5 or

IAL

I

O

O (Z)

I/O (Z)

O (Z)

I/O (Z)

I/O (Z)

I

I/O (Z)

I

I/O (Z)

I

I

O

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

I

Hi-Z

I

Hi-Z

I

Float

Float

Float

Float

Float

Float

Float

High (Inactive)

Float

High (Inactive)

Float

Low (Inactive)

BR

,

EBR

IS

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

D4 or

IS

D3 or

IACK

D2:0 or

IAD15:13

PMS

DMS

BMS

IOMS

CMS

RD

WR

BR

BG

BGH

IRQ2

/PF7

I/O (Z)

I

I/O (Z)

**

I/O (Z)

I/O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

O (Z)

I

O (Z)

O (Z)

I/O (Z)

Hi-Z

I

Hi-Z

**

Hi-Z

Hi-Z

O

O

O

O

O

O

O

I

O

O

I

BR

,

EBR

Float

High (Inactive)

Float

Float

Float

Float

Float

Float

Float

Float

Float

Float

Float

High (Inactive)

Float

Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High (Inactive)

or Program as Output,

Set to 1, Let Float

Input = High or Low,

Output = Float

High or Low

High or Low

High or Low

Float

Input = High or Low,

Output = Float

High or Low

High or Low

High or Low

Float

BR

,

EBR

BR

,

EBR

IS

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

BR

,

EBR

EE

EE

IRQL1

/PF6

I/O (Z)

I

IRQL0

/PF5

I/O (Z)

I

IRQE

/PF4

I/O (Z)

I

SCLK0

I/O

I

RFS0

DR0

TFS0

DT0

SCLK1

I/O

I

I/O

O

I/O

I

I

O

O

I

RFS1/

IRQ0

DR1/

FI

TFS1/

IRQ1

DT1/

FO

EE

EBR

EBG

ERESET

EMS

EINT

ECLK

ELIN

ELOUT

I/O

I

I/O

O

I

I

O

I

O

I

I

I

O

I

I

O

O

I

I

O

I

O

I

I

I

O

NOTES

*

*Hi-Z = High Impedance.

**Determined by MODE D pin:

Mode D = 0 and in host mode:

IACK

is an active, driven signal and cannot

be “wire ORed.”

Mode D = 1 and in host mode:

IACK

is an open source and requires an

external pull-down, but multiple

IACK

pins can be “wire ORed” together.

1.If the CLKOUT pin is not used, turn it OFF.

2.If the Interrupt/Programmable Flag pins are not used, there are two options:

Option 1: When these pins are configured as INPUTS at reset and function

as interrupts and input flag pins, pull the pins High (inactive).

Option 2: Program the unused pins as OUTPUTS, set them to 1, and let

them float.

3.All bidirectional pins have three-stated outputs. When the pins is configured

as an output, the output is Hi-Z (high impedance).

4.CLKIN, RESET, and PF3:0 are not included in the table because these pins

must be used.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-21XX4444 | ADSP-2100 Family DSP Microcomputers |

| ADSP-21MSP5859 | LM101A/LM201A/LM301A Operational Amplifiers; Package: MDIP; No of Pins: 8; Qty per Container: 40; Container: Rail |

| ADSP-21XX | ADSP-2100 Family DSP Microcomputers |

| ADSP-21MOD970-110 | Multiport Internet Gateway Processor Solution |

| ADSP-21mod970-110 | Data Pump Solution Gateway Processor Solution(多端口網(wǎng)關(guān)處理器解決方案) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-3128AJG | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| ADSP-3128ASG/883B | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-3201JG | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| ADSP-3201KG | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:MULTIPLIER, 144 Pin, Ceramic, PGA |

| ADSP-3201TG | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。