- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374035 > ADSP-2173BS-80 (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-2173BS-80 |

| 廠(chǎng)商: | ANALOG DEVICES INC |

| 元件分類(lèi): | 數(shù)字信號(hào)處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 24-BIT, 10 MHz, OTHER DSP, PQFP128 |

| 封裝: | PLASTIC, QFP-128 |

| 文件頁(yè)數(shù): | 44/52頁(yè) |

| 文件大小: | 664K |

| 代理商: | ADSP-2173BS-80 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

REV. A

–44–

ADSP-2171/ADSP-2172/ADSP-2173

ADSP-2173

CAPACIT IVE LOADING

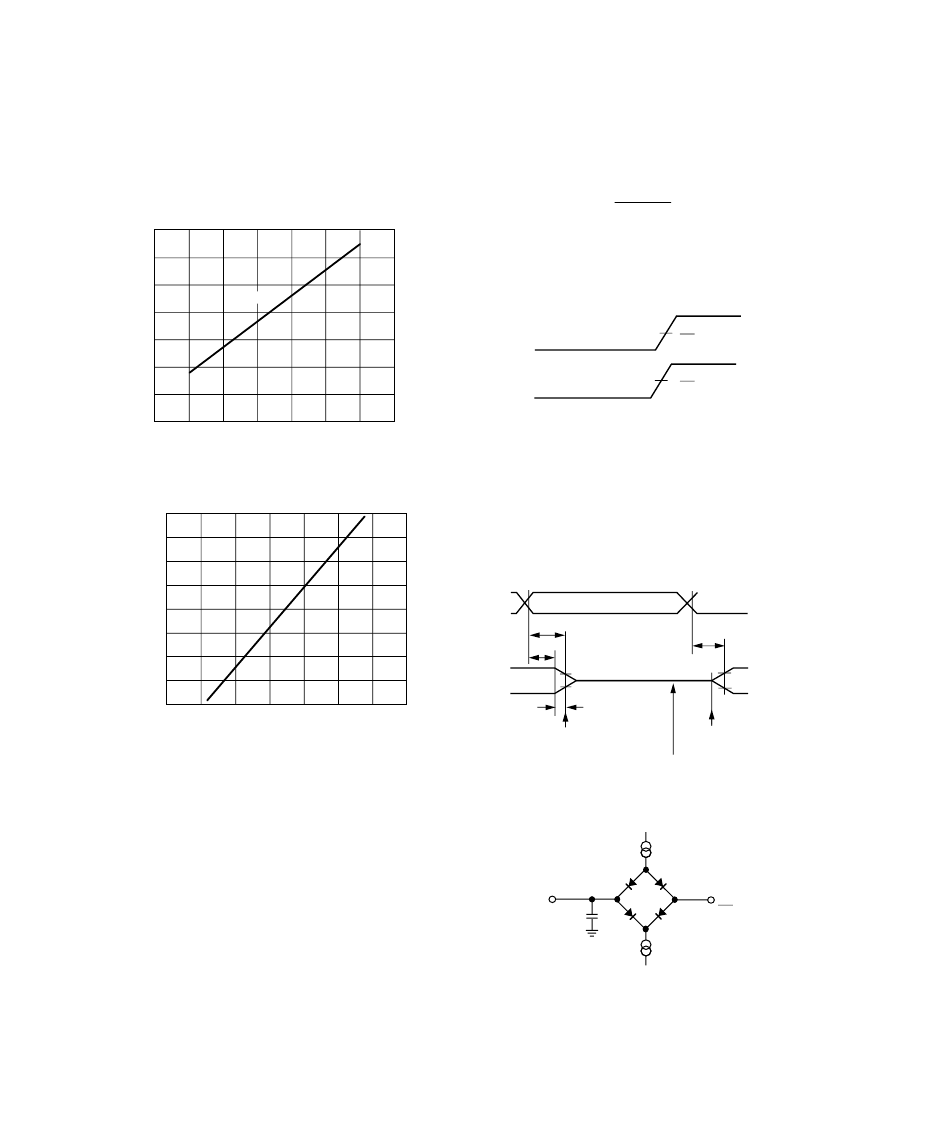

Figures 35 and 36 show the capacitive loading characteristics of

the ADSP-2173.

16

8

25

12

28

20

24

150

125

100

75

50

V

DD

= 3.3 V

C

L

– pF

R

Figure 35. Typical Output Rise Time vs. Load Capacitance,

C

L

(at Maximum Ambient Operating Temperature)

NOMINAL

-2

25

+4

+2

+8

+10

+12

150

125

100

75

50

+14

V

C

L

– pF

Figure 36. Typical Output Valid Delay or Hold vs. Load

Capacitance, C

L

(at Maximum Ambient Operating

Temperature)

T E ST CONDIT IONS

Output Disable T ime

Output pins are considered to be disabled when they have

stopped driving and started a transition from the measured out-

put high or low voltage to a high impedance state. T he output

disable time (t

DIS

) is the difference of t

MEASURED

and t

DECAY

, as

shown in the Output Enable/Disable diagram. T he time is the

interval from when a reference signal reaches a high or low volt-

age level to when the output voltages have changed by 0.5 V

from the measured output high or low voltage. T he decay time,

t

DECAY

, is dependent on the capacitative load, C

L

, and the cur-

rent load,

i

L

, on the output pin. It can be approximated by the

following equation:

t

DECAY

=

C

L

· 0.5

V

i

L

from which

t

DIS

=

t

MEASURED

±

t

DECAY

is calculated. If multiple pins (such as the data bus) are dis-

abled, the measurement value is that of the last pin to stop

driving.

INPUT

OUTPUT

V

DD

2

V

DD

2

Figure 37. Voltage Reference Levels for AC Measure-

ments (Except Output Enable/Disable)

Output E nable T ime

Output pins are considered to be enabled when that have made

a transition from a high-impedance state to when they start driv-

ing. T he output enable time (t

ENA

) is the interval from when a

reference signal reaches a high or low voltage level to when the

output has reached a specified high or low trip point, as shown

in the Output Enable/Disable diagram. If multiple pins (such as

the data bus) are enabled, the measurement value is that of the

first pin to start driving.

2.0V

1.0V

t

ENA

REFERENCE

SIGNAL

OUTPUT

t

DECAY

V

OH

(MEASURED)

OUTPUT STOPS

DRIVING

OUTPUT STARTS

DRIVING

t

DIS

t

MEASURED

V

OL

(MEASURED)

V

OH

(MEASURED) – 0.5V

V

OL

(MEASURED) +0.5V

HIGH-IMPEDANCE STATE. TEST CONDITIONS CAUSE

THIS VOLTAGE LEVEL TO BE APPROXIMATELY 1.5V.

V

OH

(MEASURED)

V

OL

(MEASURED)

Figure 38. Output Enable/Disable

TO

OUTPUT

PIN

50pF

I

OH

I

OL

V

DD

2

Figure 39. Equivalent Device Loading for AC Measure-

ments (Including All Fixtures)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-2171 | DSP Microcomputer(DSP 微計(jì)算機(jī)) |

| ADSP-2172 | DSP Microcomputer(DSP 微計(jì)算機(jī)) |

| ADSP-2173 | DSP Microcomputer(DSP 微計(jì)算機(jī)) |

| ADSP-2181BS-115 | DSP Microcomputer |

| ADSP-2181BS-133 | DSP Microcomputer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2173BST-80 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 20MHz 20MIPS 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:16BIT FXD PT PROC 3.3V - Bulk |

| ADSP-2176-760040 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760061 | 制造商:Analog Devices 功能描述: |

| ADSP-2176-760243 | 制造商:Analog Devices 功能描述: |

| ADSP-2178-780244 | 制造商:AD 制造商全稱(chēng):Analog Devices 功能描述:GSM Baseband Processing Chipset |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。