- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375263 > ADS1226IRGVR (Analog Devices, Inc.) 24-Bit Analog-to-Digital Converter with One- and Two-Channel Differential Inputs and Internal Oscillator PDF資料下載

參數(shù)資料

| 型號: | ADS1226IRGVR |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 24-Bit Analog-to-Digital Converter with One- and Two-Channel Differential Inputs and Internal Oscillator |

| 中文描述: | 24位模擬數(shù)字轉(zhuǎn)換器與單和雙通道差分輸入和內(nèi)部振蕩器 |

| 文件頁數(shù): | 15/24頁 |

| 文件大?。?/td> | 398K |

| 代理商: | ADS1226IRGVR |

www.ti.com

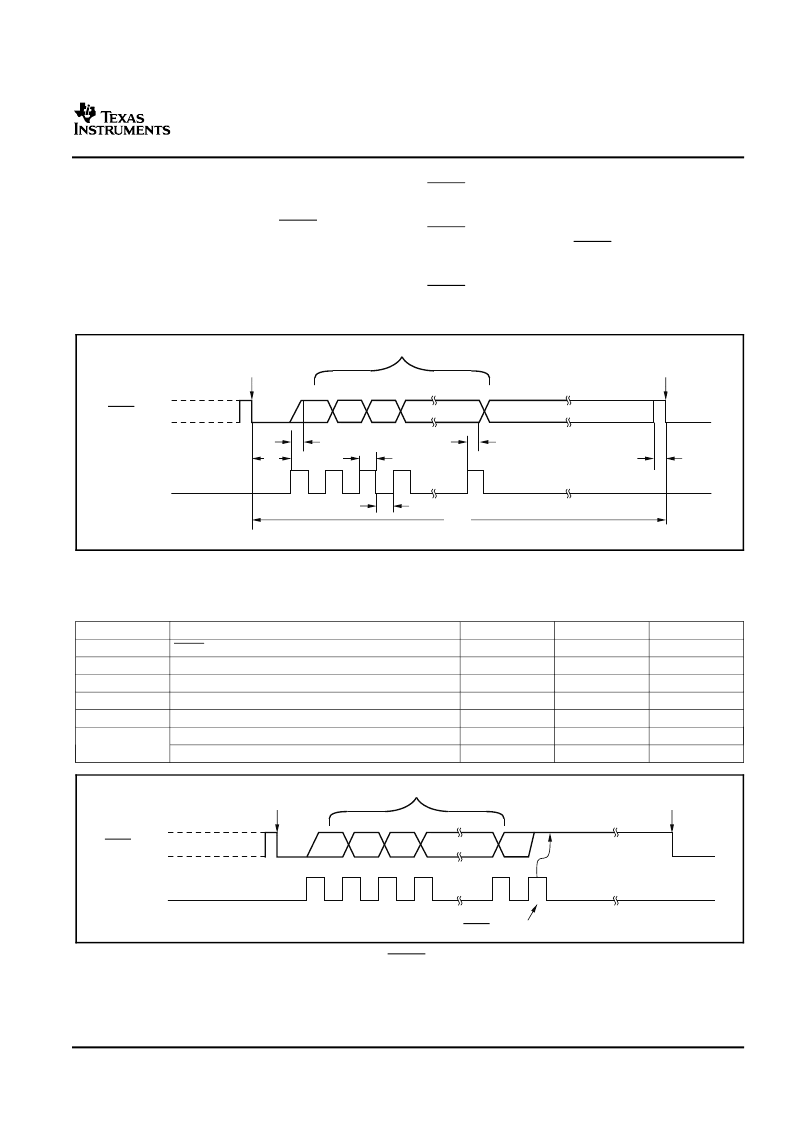

DATA RETRIEVAL

With the START pin high, the ADS1225 and

ADS1226 continuously convert the analog input

signal. To retrieve data, wait until DRDY/DOUT goes

low, as illustrated in

Figure 28

and

Table 5

. After this

occurs, begin shifting out the data by applying

SCLKs. Data is shifted out MSB first. It is not

required to shift out all 24 bits of data, but the data

must be retrieved before the new data is updated

(see t

2

) or else it will be overwritten.

DRDY/DOUT

23

22

21

1

24

0

LSB

MSB

Data

Data Ready

SCLK

START Tied High

t

DS

t

CONV

t

SCLK

t

SCLK

t

UP

New Data Ready

t

PD

t

HD

23

1

24

25

22

21

0

Data

25th SCLK to Force

/DOUT High

DRDY

Data Ready

New Data Ready

DRDY/DOUT

SCLK

ADS1225

ADS1226

SBAS346–MAY 2006

Avoid

DRDY/DOUT remain at the state of the last bit

shifted out until it is taken high (see t

6

), indicating

that new data is being updated. To avoid having

DRDY/DOUT remain in the state of the last bit, shift

a 25th SCLK to force DRDY/DOUT high (refer to

Figure 29

). This technique is useful when a host

controlling the ADS1225 and ADS1226 is polling

DRDY/DOUT to determine when data is ready.

data

retrieval

during

the

update

period.

Figure 28. Data Retrieval Timing

Table 5. Data Retrieval Times for

Figure 28

SYMBOL

t

DS

t

SCLK

t

PD

t

HD

t

UP

t

CONV

DESCRIPTION

DRDY/DOUT low to first SCLK rising edge

SCLK positive or negative pulse width

SCLK rising edge to new data bit valid: propagation delay

SCLK rising edge to old data bit valid: hold time

Data updating: no readback allowed

Conversion time (1/data rate), High-Speed mode

Conversion time (1/data rate), High-Resolution mode

MIN

0

100

MAX

UNITS

ns

ns

ns

ns

μ

s

ms

ms

50

0

29.5

8.0

45.5

49.2

13.3

83.3

Figure 29. Data Retrieval with DRDY/DOUT Forced High Afterwards

15

Submit Documentation Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADS1226IRGVRG4 | 24-Bit Analog-to-Digital Converter with One- and Two-Channel Differential Inputs and Internal Oscillator |

| ADS1226IRGVT | 24-Bit Analog-to-Digital Converter with One- and Two-Channel Differential Inputs and Internal Oscillator |

| ADS1226IRGVTG4 | 24-Bit Analog-to-Digital Converter with One- and Two-Channel Differential Inputs and Internal Oscillator |

| ADS1245 | Low-Power, 24-Bit Analog-to-Digital Converter |

| ADS1245IDGSR | Low-Power, 24-Bit Analog-to-Digital Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADS1226IRGVRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 24-Bit ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADS1226IRGVT | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 24-Bit ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADS1226IRGVT | 制造商:Texas Instruments 功能描述:A/D Converter (A-D) IC |

| ADS1226IRGVTG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 24-Bit ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADS122C04EVM | 功能描述:ADS122C04EVM 制造商:texas instruments 系列:* 零件狀態(tài):在售 標準包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復。