- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373980 > ADE7759ARS (ANALOG DEVICES INC) 8-Channel 14-Bit Single-Supply Voltage-Output DAC; Package: LQFP (10x10mm); No of Pins: 52; Temperature Range: Industrial PDF資料下載

參數(shù)資料

| 型號(hào): | ADE7759ARS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 英文描述: | 8-Channel 14-Bit Single-Supply Voltage-Output DAC; Package: LQFP (10x10mm); No of Pins: 52; Temperature Range: Industrial |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| 封裝: | SSOP-20 |

| 文件頁數(shù): | 28/32頁 |

| 文件大小: | 530K |

| 代理商: | ADE7759ARS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁

REV. 0

ADE7759

–28–

Table IV. Register List

Address

Name

R/W

# of Bits

Default

Description

01h

WAVEFORM

R

24/40

0h

The Waveform register is a read-only register. This register contains

the sampled waveform data from Channel 1, Channel 2, or the Active

Power signal. The data source and the length of the Waveform regis-

ters are selected by data bits 14 and 13 in the Mode Register—see

Channel 1 and 2 Sampling section.

The Active Energy Register. Active Power is accumulated (Integrated)

over time in this 40-bit, read-only register. The energy register can hold

a minimum of 11.53 seconds of Active Energy information with full-

scale analog inputs before it overflows—see Energy Calculation section.

Same as the Active Energy Register except that the register is reset to 0

following a read operation.

Interrupt Status Register. This is an 8-bit read-only register. The status

register contains information regarding the source of ADE7759 inter-

rupts—see Interrupts section.

Same as the Interrupt Status Register except that the register contents

are reset to 0 (all flags cleared) after a read operation.

The Mode Register. This is a 16-bit register through which most of the

ADE7759 functionality is accessed. Signal sample rates, filter enabling

and calibration modes are selected by writing to this register. The

contents may be read at any time—see Mode Register section.

CF Frequency Divider Denominator Register. The output frequency

on the CF pin is adjusted by writing to this 12-bit read/write register—

see Energy-to-Frequency Conversion section.

Channel 1 Offset Adjust. The MSB is used to enable the digital integra-

tor. Bit 6 is not used. Writing to Bit 0 to 5 allows offsets on Channel 1

to be removed—see Analog Inputs

section and

CH1OS Register section.

Channel 2 Offset Adjust. Writing to this 6-bit register allows any offsets

on Channel 2 to be removed—see Analog Inputs section.

PGA Gain Adjust. This 8-bit register is used to adjust the gain selec-

tion for the PGA in Channel 1 and 2—see Analog Inputs section.

Active Power Gain Adjust. This is a 12-bit register. The Active Power

calculation can be calibrated by writing to this register. The calibration

range is

±

50% of the nominal full-scale active power. The resolution of the

gain adjust is 0.0244%/LSB—see Channel 1 ADC Gain Adjust section.

Phase Calibration Register. The phase relationship between Channel 1

and Channel 2 can be adjusted by writing to this 8-bit register. The

valid content of this two’s complement register is between 9Eh and

5Ch, which is a phase difference of –2.365

°

to +2.221

°

at 60 Hz in

0.0241

°

steps—see Phase Compensation section.

Active Power Offset Correction. This 16-bit register allows small off-

sets in the Active Power calculation to be removed—see Active Power

Calculation section.

02h

AENERGY

R

40

0h

03h

RSTENERGY

R

40

0h

04h

STATUS

R

8

40h

05h

RSTSTATUS

R

8

0h

06h

MODE

R/W

16

000Ch

07h

CFDEN

R/W

12

3Fh

08h

CH1OS

R/W

8

80h

09h

CH2OS

R/W

6

0h

0Ah

GAIN

R/W

8

0h

0Bh

APGAIN

R/W

12

0h

0Ch

PHCAL

R/W

8

0h

0Dh

APOS

R/W

16

0h

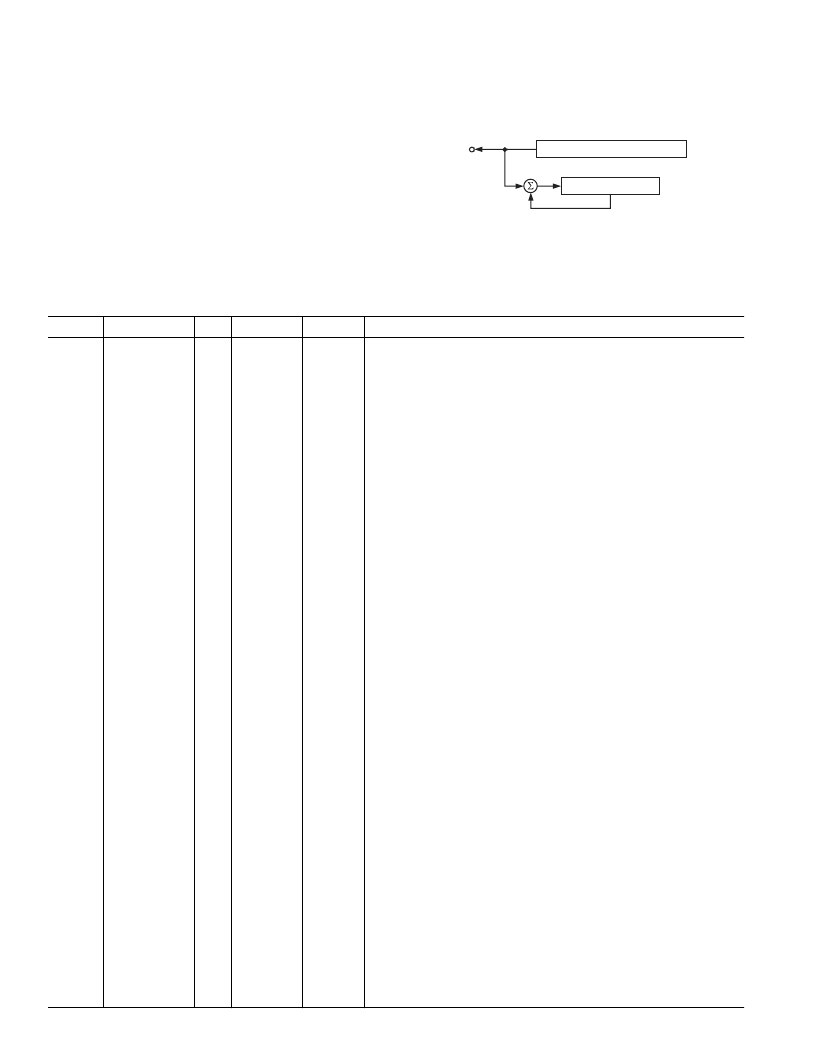

CHECKSUM REGISTER

The ADE7759 has a Checksum register (CHKSUM[5:0]) to

ensure the data bits received in the last serial read operation are

not corrupted. The 6-bit Checksum register is reset before the

first bit (MSB of the register to be read) is put on the DOUT

pin. During a serial read operation, when each data bit becomes

available on the rising edge of SCLK, the bit will be added to

the Checksum register. In the end of the serial read operation,

the content of the Checksum register will be the sum of all the ones

contained in the register previously read. Using the Checksum

register, the user can determine if an error has occurred during

the last read operation.

Note that a read to the CHKSUM register will also generate a

checksum of the CHKSUM register itself.

CONTENT OF REGISTER (n-bytes)

CHECKSUM REGISTER

ADDR: 1Eh

+

+

DOUT

Figure 47. Checksum Register for Serial Interface Read

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADE7759 | Active Energy Metering IC with di/dt Sensor Interface |

| ADE7760ARSRL | Energy Metering IC with On-Chip Fault Detection |

| ADE7760 | 8-Channel 14-Bit Single-Supply Voltage-Output DAC; Package: LQFP (10x10mm); No of Pins: 52; Temperature Range: Industrial |

| ADE7760ARS | Energy Metering IC with On-Chip Fault Detection |

| ADE7762 | Polyphase Energy Metering IC with Phase Drop Indication |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADE7759ARSRL | 功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:否 類別:集成電路 (IC) >> PMIC - 能量測量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

| ADE7759ARSZ | 功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

| ADE7759ARSZRL | 功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

| ADE7760 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Energy Metering IC with On-Chip Fault Detection |

| ADE7760ARS | 制造商:Analog Devices 功能描述:Energy Measurement 20-Pin SSOP 制造商:Analog Devices 功能描述:ENERGY METER IC W/ ONCHIP FAULT & OSCIL. - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。