- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373959 > AD9212BCPZ-65 (ANALOG DEVICES INC) Octal, 10-Bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter PDF資料下載

參數(shù)資料

| 型號: | AD9212BCPZ-65 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Octal, 10-Bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| 中文描述: | 8-CH 10-BIT FLASH METHOD ADC, SERIAL ACCESS, QCC64 |

| 封裝: | 9 X 9 MM, ROHS COMPLIANT, MO-220VMMD-4, LFCSP-64 |

| 文件頁數(shù): | 25/56頁 |

| 文件大小: | 1840K |

| 代理商: | AD9212BCPZ-65 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

AD9212

Rev. 0 | Page 25 of 56

500

400

300

200

100

–500

–400

–300

–200

–100

0

–1.0ns

–1.5ns

–0.5ns

0ns

0.5ns

1.0ns

1.5ns

E

EYE: ALL BITS

ULS: 12071/12071

90

50

10

20

30

40

60

70

80

–0

–100ps

–50ps

0ps

50ps

100ps

150ps

T

0

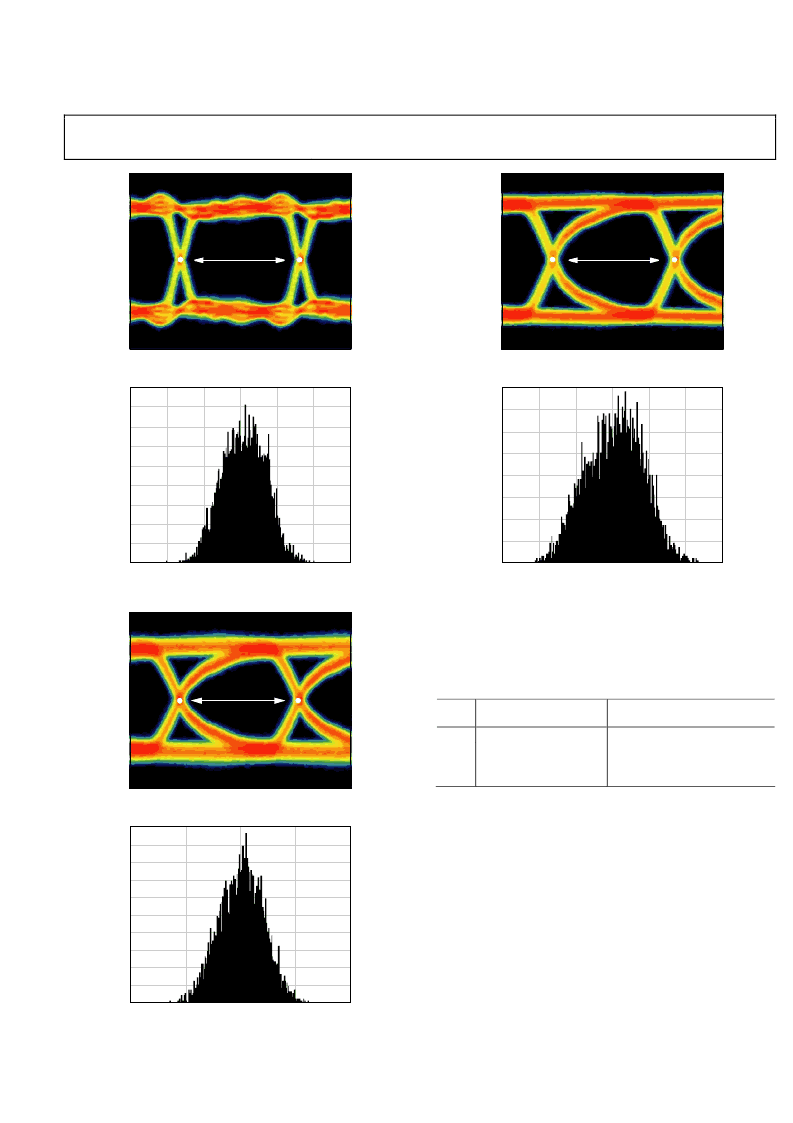

Figure 60. Data Eye for LVDS Outputs in ANSI Mode with Trace Lengths Less

than 24 Inches on Standard FR-4

60

80

90

70

50

40

20

10

100

30

–0

–100ps

100ps

0ps

200ps

T

500

400

300

200

100

–500

–400

–300

–200

–100

0

–1.0ns

–0.5ns

0ns

0.5ns

1.5ns

–1.5ns

1.0ns

E

EYE: ALL BITS

ULS: 12067/12067

0

Figure 61. Data Eye for LVDS Outputs in ANSI Mode with Trace Lengths

Greater than 24 Inches on Standard FR-4

400

300

200

100

–400

–300

–200

–100

0

–0.5ns

0ns

0.5ns

E

EYE: ALL BITS

ULS: 12072/12072

80

50

10

20

30

40

60

70

–0

–100ps

–50ps

0ps

50ps

100ps

150ps

T

–1.0ns

1.5ns

–1.5ns

1.0ns

0

Figure 62. Data Eye for LVDS Outputs in ANSI Mode with 100 Ω Termination

on and Trace Lengths Greater than 24 Inches on Standard FR-4

The format of the output data is offset binary by default. An

example of the output coding format can be found in Table 8.

If it is desired to change the output data format to twos

complement, see the Memory Map section.

Table 8. Digital Output Coding

(VIN+) (VIN), Input

Span = 2 V p-p (V)

1023

+1.00

512

0.00

511

0.001953

0

1.00

Code

Digital Output Offset Binary (D9

... D0)

11 1111 1111

10 0000 0000

01 1111 1111

00 0000 0000

Data from each ADC is serialized and provided on a separate

channel. The data rate for each serial stream is equal to 10 bits

times the sample clock rate, with a maximum of 650 Mbps

(10 bits × 65 MSPS = 650 Mbps). The lowest typical conversion

rate is 10 MSPS. However, if lower sample rates are required for

a specific application, the PLL can be set up for encode rates

lower than 10 MSPS via the SPI. This allows encode rates as low

as 5 MSPS. See the Memory Map section to enable this feature.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9212BCPZRL7-40 | Octal, 10-Bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9212BCPZRL7-65 | Octal, 10-Bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9214 | 10-Bit, 65/80/105 MSPS 3 V A/D Converter |

| AD9214-105PCB | 10-Bit, 65/80/105 MSPS 3 V A/D Converter |

| AD9214-65PCB | 10-Bit, 65/80/105 MSPS 3 V A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9212BCPZRL7-40 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Octal, 10-Bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9212BCPZRL7-65 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Octal, 10-Bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9214 | 制造商:AD 制造商全稱:Analog Devices 功能描述:10-Bit, 65/80/105 MSPS 3 V A/D Converter |

| AD9214-105PCB | 制造商:Analog Devices 功能描述:10 BIT 105MSPS A/D CONV. EVAL BOARD - Bulk |

| AD9214-65PCB | 制造商:Analog Devices 功能描述:10 BIT 65 MSPS A/D CONVERTER EVAL BOARD - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。