- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373959 > AD9200JSTRL (ANALOG DEVICES INC) Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter PDF資料下載

參數(shù)資料

| 型號: | AD9200JSTRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Complete 10-Bit, 20 MSPS, 80 mW CMOS A/D Converter |

| 中文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| 封裝: | PLASTIC, LQFP-48 |

| 文件頁數(shù): | 6/24頁 |

| 文件大?。?/td> | 338K |

| 代理商: | AD9200JSTRL |

AD9200

–6–

REV. E

DEFINITIONS OF SPECIFICATIONS

Integral Nonlinearity (INL)

Integral nonlinearity refers to the deviation of each individual

code from a line drawn from “zero” through “full scale”. The

point used as “zero” occurs 1/2 LSB before the first code transi-

tion. “Full scale” is defined as a level 1 1/2 LSB beyond the last

code transition. The deviation is measured from the center of

each particular code to the true straight line.

Differential Nonlinearity (DNL, No Missing Codes)

An ideal ADC exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. It is often

specified in terms of the resolution for which no missing codes

(NMC) are guaranteed.

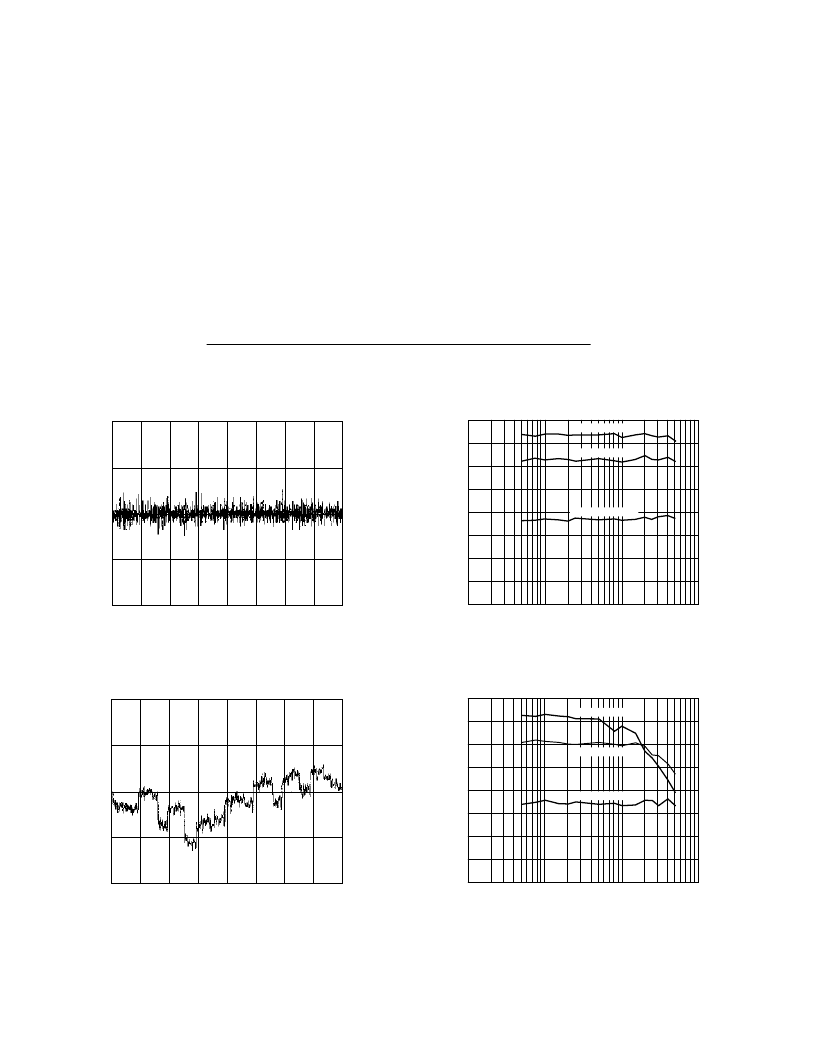

Typical Characterization Curves

CODE OFFSET

1.0

0.5

–1.00

1024

128

D

256

384

512

640

768

896

0

–0.5

Figure 3. Typical DNL

CODE OFFSET

1.0

0.5

–1.00

1024

128

I

256

384

512

640

768

896

0

–0.5

Figure 4. Typical INL

Offset Error

The first transition should occur at a level 1 LSB above “zero.”

Offset is defined as the deviation of the actual first code transi-

tion from that point.

Gain Error

The first code transition should occur for an analog value 1 LSB

above nominal negative full scale. The last transition should

occur for an analog value 1 LSB below the nominal positive full

scale. Gain error is the deviation of the actual difference be-

tween first and last code transitions and the ideal difference

between the first and last code transitions.

Pipeline Delay (Latency)

The number of clock cycles between conversion initiation and

the associated output data being made available. New output

data is provided every rising edge.

INPUT FREQUENCY – Hz

60

55

120

1.00E+08

1.00E+06

1.00E+07

50

45

25

40

35

30

S

–0.5 AMPLITUDE

–6.0 AMPLITUDE

–20.0 AMPLITUDE

Figure 5. SNR vs. Input Frequency

60

55

120

1.00E+08

1.00E+06

INPUT FREQUENCY – Hz

S

1.00E+07

50

45

25

40

35

30

–0.5 AMPLITUDE

–6.0 AMPLITUDE

–20.0 AMPLITUDE

Figure 6. SINAD vs. Input Frequency

(AVDD = +3 V, DRVDD = +3 V, F

S

= 20 MHz (50% Duty Cycle), MODE = AVDD, 2 V Input

Span from 0.5 V to 2.5 V, External Reference, unless otherwise noted)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9201 | Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC |

| AD9201-EVAL | Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC |

| AD9201ARS | Dual Channel, 20 MHz 10-Bit Resolution CMOS ADC |

| AD9201EVALBOARD | Octal I2C 16-Bit Rail-to-Rail DACs in 16-Lead SSOP; Package: SSOP; No of Pins: 16; Temperature Range: -40°C to +85°C |

| AD9203 | 10-Bit, 40 MSPS, 3 V, 74 mW A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9200JSTZ | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| AD9200KST | 制造商:Rochester Electronics LLC 功能描述:10-BIT 20 MSPS, 80 MW CMOS A/D CONVERTER - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9200KSTRL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel 制造商:Analog Devices 功能描述: |

| AD9200KSTZ | 制造商:Analog Devices 功能描述:ADC SGL PIPELINED 20MSPS 10-BIT PARALLEL 48LQFP - Trays |

| AD9200KSTZRL | 制造商:Analog Devices 功能描述:ADC SGL PIPELINED 20MSPS 10-BIT PARALLEL 48LQFP - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。