- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25570 > 9LPRS502YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 PDF資料下載

參數(shù)資料

| 型號(hào): | 9LPRS502YGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件頁(yè)數(shù): | 2/29頁(yè) |

| 文件大?。?/td> | 279K |

| 代理商: | 9LPRS502YGLFT |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

IDTTM/ICSTM

56-pin CK505 w/Fully Integrated Voltage Regulator + Integrated Series Resistor

1125E—02/26/09

Advance Information

ICS9LPRS502

56-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR + INTEGRATED SERIES RESISTOR

10

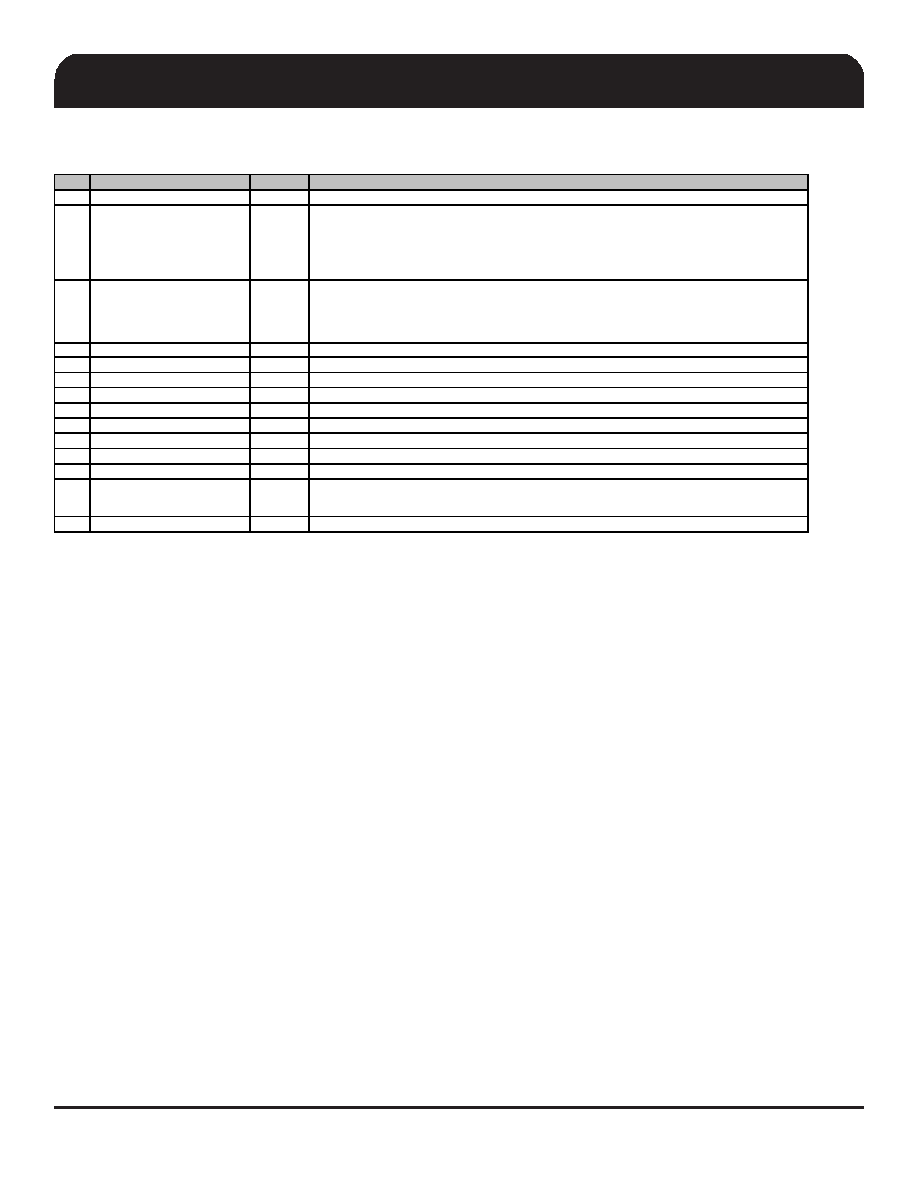

MLF Pin Description (Continued)

PIN #

PIN NAME

TYPE

DESCRIPTION

43

VDDSRC_IO

PWR

Power supply for SRC outputs. 1.05 to 3.3V +/-5%.

44

CPUC2_ITP/SRCC8

OUT

Complement clock of low power differential CPU2/Complement clock of differential SRC pair. The function of this

pin is determined by the latched input value on pin 7, PCIF5/ITP_EN on powerup. The function is as follows:

Pin 7 latched input Value

0 = SRC8#

1 = ITP#

45

CPUT2_ITP/SRCT8

OUT

True clock of low power differential CPU2/True clock of differential SRC pair. The function of this pin is determined

by the latched input value on pin 7, PCIF5/ITP_EN on powerup. The function is as follows:

Pin 7 latched input Value

0 = SRC8

1 = ITP

46

NC

Not Connected

47

VDDCPU_IO

PWR

Power supply for CPU outputs. 1.05 to 3.3V +/-5%.

48

CPUC1_F

OUT

Complement clock of low power differenatial CPU clock pair. This clock will be free-running during iAMT.

49

CPUT1_F

OUT

True clock of low power differential CPU clock pair. This clock will be free-running during iAMT.

50

GNDCPU

PWR

Ground Pin for CPU Outputs

51

CPUC0

OUT

Complement clock of low power differential CPU clock pair.

52

CPUT0

OUT

True clock of low power differential CPU clock pair.

53

VDDCPU

PWR

Power Supply 3.3V nominal.

54

CK_PWRGD/PD#

IN

Notifies CK505 to sample latched inputs, or iAMT entry/exit, or PWRDWN# mode

55

FSLB/TEST_MODE

IN

3.3V tolerant input for CPU frequency selection. Refer to input electrical characteristics for Vil_FS and Vih_FS

values. TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test mode. Refer

to Test Clarification Table.

56

GNDREF

PWR

Ground pin for crystal oscillator circuit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9LPRS502YKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC56 |

| 9LPRS511EGLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 9LPRS525AFLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

| 9LPRS535BFLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9LPRS535CFLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9LPRS502YKLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:56-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR + INTEGRATED SERIES RESISTOR |

| 9LPRS509HGLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS509HGLF LOGIC AND TIMING MISC - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS509HGLF Logic and Timing Misc |

| 9LPRS509PGLF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPRS509PGLFT | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK 制造商:Integrated Device Technology Inc 功能描述:64 TSSOP (LEAD FREE) - Tape and Reel |

| 9LPRS511EGLF | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。