- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25515 > 952601YGLFT (INTEGRATED DEVICE TECHNOLOGY INC) PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | 952601YGLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, ROHS COMPLIANT, MO-153, TSSOP-56 |

| 文件頁數(shù): | 8/25頁 |

| 文件大小: | 227K |

| 代理商: | 952601YGLFT |

IDTTM

Progammable Timing Control HubTM for Next Gen P4TM Processor

701J—01/25/10

ICS952601

Programmable Timing Control HubTM for Next Gen P4TM Processor

16

PD# is an asynchronous active low input used to shut off all clocks cleanly prior to clock power.

When PD# is asserted low all clocks will be driven low before turning off the VCO. In PD# de-assertion all clocks will start

without glitches.

PD#, Power Down

#

N

W

D

R

W

PU

P

C#

U

P

CC

R

S#

C

R

S6

6

V

3I

C

P

/

F

I

C

PT

O

D

/

B

S

UF

E

Re

t

o

N

1l

a

m

r

o

Nl

a

m

r

o

Nl

a

m

r

o

Nl

a

m

r

o

Nz

H

M

6

6z

H

M

3

3z

H

M

8

4z

H

M

8

1

3

.

4

1

0r

o

2

*

f

e

r

I

t

a

o

l

F

t

a

o

l

F2

*

f

e

r

I

t

a

o

l

F

r

o

t

a

o

l

Fw

o

Lw

o

Lw

o

Lw

o

L

Notes:

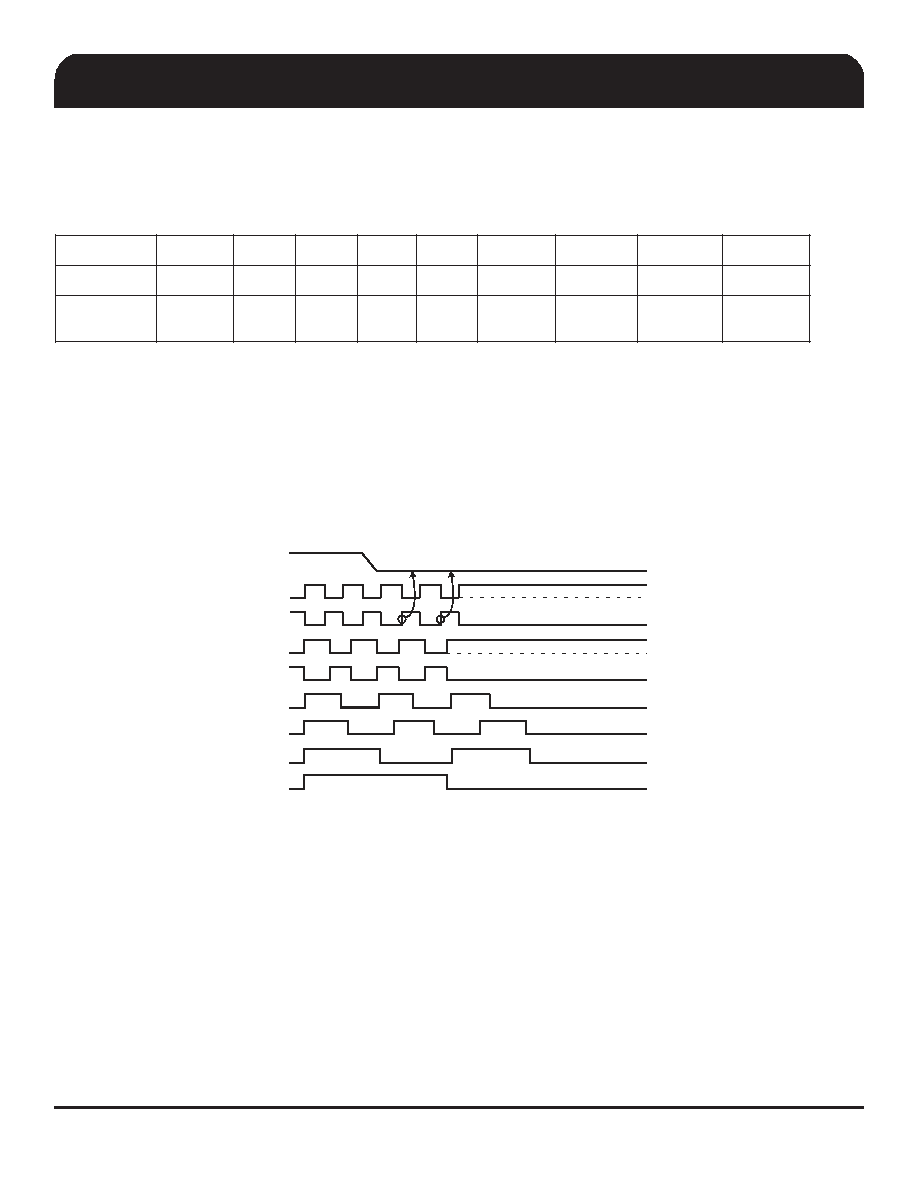

1. Refer to tristate control of CPU and SRC clocks in section 7.7 for tristate timing and operation.

2. Refer to Control Registers in section 16 for CPU_Stop, SRC_Stop and PwrDwn SMBus tristate control addresses.

PD# should be sampled low by 2 consecutive CPU# rising edges before stopping clocks. All single ended clocks will be

held low on their next high to low transition.

All differential clocks will be held high on the next high to low transition of the complimentary clock. If the control register

determining to drive mode is set to 'tri-state', the differential pair will be stopped in tri-state mode, undriven.

When the drive mode but corresponding to the CPU or SRC clock of interest is set to '0' the true clock will be driven high at

2 x Iref and the complementary clock will be tristated. If the control register is programmed to '1' both clocks will be tristated.

PWRDWN#

CPU, 133MHz

CPU#, 133MHz

SRC, 100MHz

SRC#, 100MHz

3V66, 66MHz

USB, 48MHz

PCI, 33MHz

REF, 14.31818

PD# Assertion

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 952601YFLFT | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 952703BF | 217.9 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952801CFLFT | 293.34 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 952807 | MODULAR TERMINAL BLOCK |

| 9528090000 | 10 A, MODULAR TERMINAL BLOCK, 1 DECK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 952606PFLF | 制造商:Integrated Device Technology Inc 功能描述:Programmable PLL Clock Synthesizer Dual 48-Pin SSOP Tube |

| 9526-1000-60 | 制造商:Belden Inc 功能描述:Shielded Paired Cable Number of Conducto |

| 952618BFLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF GENERAL PURPOSE SEMICONDUCTORS - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 952618BFLF General Purpose Semiconductors |

| 952620CFLF | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

| 952620CFLFT | 制造商:Integrated Device Technology Inc 功能描述:PC MAIN CLOCK |

發(fā)布緊急采購,3分鐘左右您將得到回復。