- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24812 > 935263912551 (NXP SEMICONDUCTORS) 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 935263912551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), 400M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, 1 MM HEIGHT, PLASTIC, SOT-386-1, TQFP-100 |

| 文件頁(yè)數(shù): | 17/56頁(yè) |

| 文件大?。?/td> | 277K |

| 代理商: | 935263912551 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

Philips Semiconductors

Preliminary specification

PDI1394L21

1394 full duplex AV link layer controller

2000 Jun 06

24

12.5.3

Interrupts

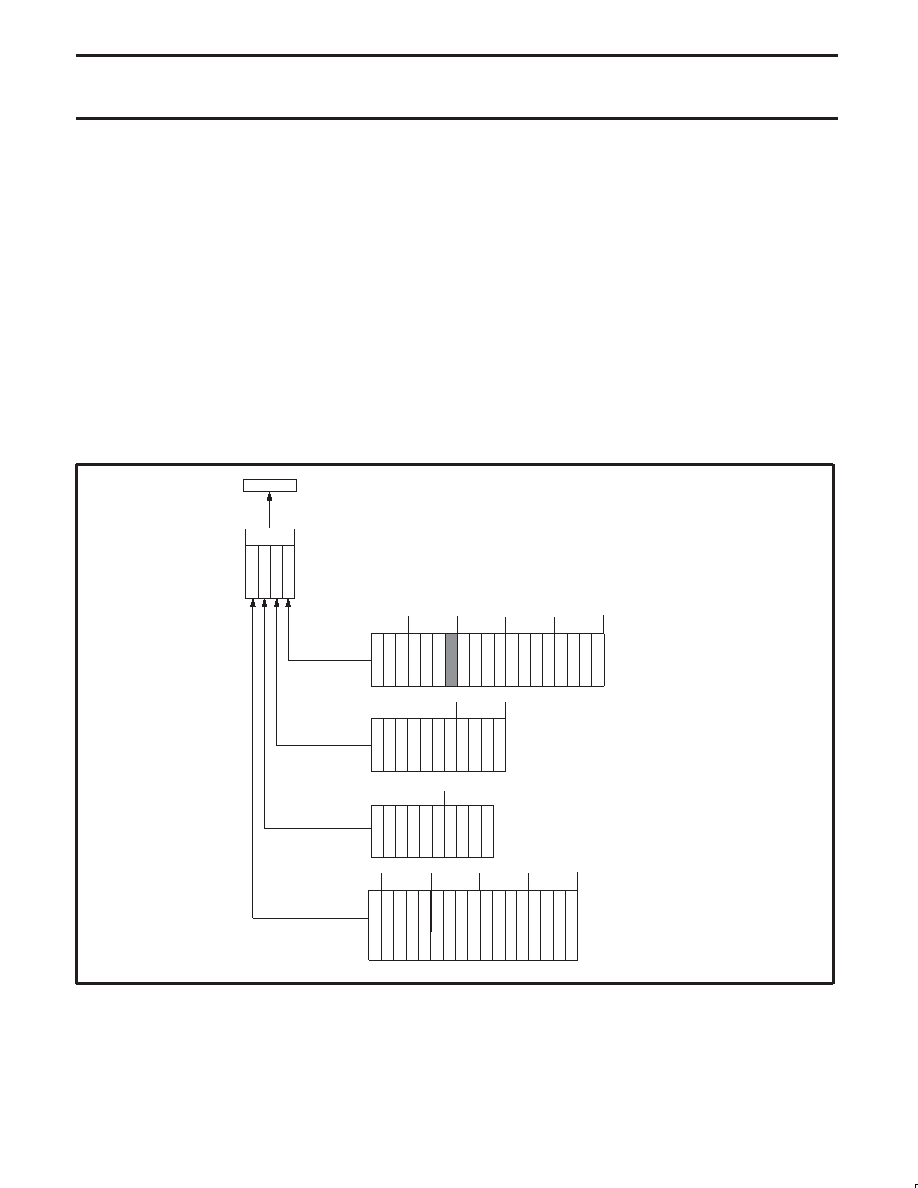

The PDI1394L21 provides a single interrupt line (HIF INT_N) for connection to a host controller. Status indications from four major areas of the

device are collected and ORed together to activate HIF INT_N. Status from four major areas of the device are collected in four status registers;

LNKPHYINTACK, ITXINTACK, IRXINTACK, and ASYINTACK. At this level, each individual status can be enabled to generate a chip-level

interrupt by activating HIF INT_N. To aid in determining the source of a chip-level interrupt, the major area of the device generating an interrupt

is indicated in the lower 4 bits of the GLOBCSR register. These bits are non-latching Read-Only status bits and do not need to be

acknowledged. To acknowledge and clear a standing interrupt, the bit in LNKPHYINTACK, ITXINTACK, IRXINTACK, or ASYINTACK causing

the interrupt status has to be written to a logic ‘1’; Note: Writing a value of ‘0’ to the bit has no effect.

12.5.3.1

Determining and Clearing Interrupts

When responding to an interrupt event generated by the PDI1394L21, or operating in polled mode, the first register examined is the GLOBCSR

register. The least significant nibble contains interrupt status bits from general sections of the device; the link layer controller, the AV transmitter,

the AV receiver, and the asynchronous transceiver. The bits in GLOBCSR[3:0] are self clearing status bits. They represent the logical OR of all

the enabled interrupt status bits in their section of the AV Link Layer Controller.

Once an interrupt, or status is detected in GLOBCSR, the appropriate interrupt status register needs to be read, see the Interrupt Hierarchy

diagram for more detail. After all the interrupt indications are dealt with in the appropriate interrupt status register, the interrupt status indication

will automatically clear in the GLOBCSR.

All interrupt status bits in the various interrupt status registers are latching unless otherwise noted.

12.5.3.2

Interrupt Hierarchy

18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SV01076

765 4 3 2 1 0

32 10

ITXINTACK (0x02C)

IRXINTACK (0x04C)

ASYINTACK (0x0A0)

LNKPHYINTACK (0x008)

GLOBCSR (0x018)

HIF INT_N

PHYINT

CMDRST

F

AIRGAP

PHYRRX

ITBADFMT

PHYRST

A

TBADFMT

SNT_REJ

HDRERR

ARBGAP

CYST

AR

T

TCERR

CYTMOUT

CYDONE

CYPEND

CYLOST

CYSEC

INPERR

TRMSYT

TRMBP

DISCARD

ITXFULL

ITXEMPTY

DBCERR

SEQERR

IRXFULL

IRXEMPTY

CRCERR

CIPT

AGFL

T

RCVBP

FSYNC

SQOV

ASYTX/RX

ITXINT

IRXINT

LNKPHYINT

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TIMEOUT

RCVDRSP

RRSPQFULL

RREQQFULL

RREQQQA

V

RRSPQRDERR

RREQQRDERR

RRSPQQA

V

SIDQA

V

RREQQLASTQ

TRSPQFULL

RRSPQLASTQ

TREQQWRERR

TRSPQWR

TRSPQWRERR

TREQQFULL

TREQQWR

65 4 3 2 1 0

RxDA

T

A

IR512LFT

8

IR256LFT

9

7

IT512LFT

IT256LFT

8

IR100LFT

10

IT100LFT

9

Figure 24. Interrupt Hierarchy

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 08-1101-00 | DREHSCHALTER 1POL 12STELLUNGEN |

| 08-1260-00 | ************GESTRICHEN************ |

| 08-1341-00 | DREHSCHALTER 3POL 4STELLUNGEN |

| 08-2101-00 | DREHSCHALTER 2POL 12STELLUNGEN |

| 08-2261-00 | DREHSCHALTER 4POL 6STELLUNGEN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。