- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360465 > 74HC195 (NXP Semiconductors N.V.) 4-bit parallel access shift register PDF資料下載

參數(shù)資料

| 型號: | 74HC195 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 4-bit parallel access shift register |

| 中文描述: | 4位并行存取移位寄存器 |

| 文件頁數(shù): | 6/9頁 |

| 文件大小: | 67K |

| 代理商: | 74HC195 |

December 1990

6

Philips Semiconductors

Product specification

4-bit parallel access shift register

74HC/HCT195

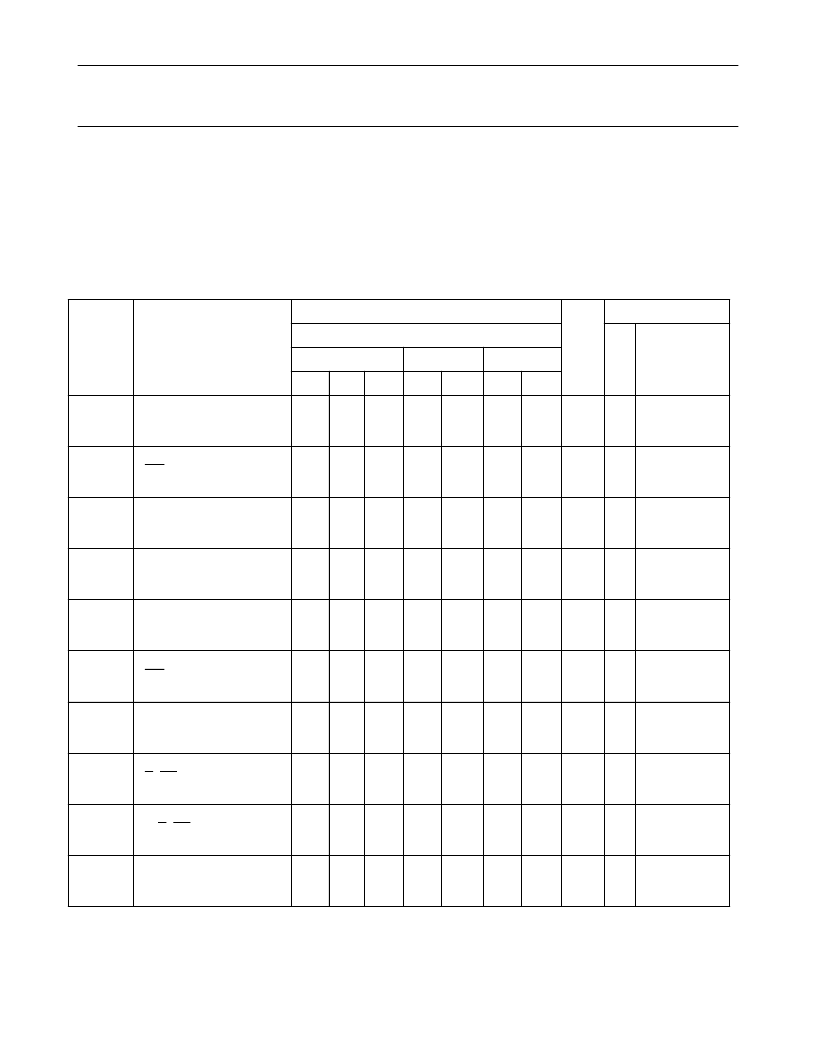

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see

“74HC/HCT/HCU/HCMOS Logic Family Specifications”

.

Output capability: standard

I

CC

category: MSI

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL PARAMETER

T

amb

(

°

C)

UNIT

TEST CONDITIONS

74HC

V

CC

(V)

WAVEFORMS

+

25

40 to

+

85

40 to

+

125

min.

typ.

max. min.

max.

min.

max.

t

PHL

/ t

PLH

propagation delay

CP to Q

n

50

18

14

41

15

12

19

7

6

17

6

5

11

4

3

17

6

5

33

12

10

25

9

7

8

3

2

17

52

62

150

30

26

150

30

26

75

15

13

190

38

33

190

38

33

95

19

16

225

45

38

225

45

38

110

22

19

ns

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

Fig.6

t

PHL

propagation delay

MR to Q

n

ns

Fig.8

t

THL

/ t

TLH

output transition time

ns

Fig.6

t

W

clock pulse width

HIGH or LOW

80

16

14

80

16

14

80

16

14

100

20

17

80

16

14

3

3

3

6

30

35

100

20

17

100

20

17

100

20

17

125

25

21

100

20

17

3

3

3

5

24

28

120

24

20

120

24

20

120

24

20

150

30

26

120

24

20

3

3

3

4

20

24

ns

Fig.6

t

W

master reset pulse width

LOW

ns

Fig.8

t

rem

removal time

MR to CP

ns

Fig.8

t

su

set-up time

J to CP

ns

Figs 8 and 9

t

su

set-up time

K, PE, D

n

to CP

ns

Figs 8 and 9

t

h

hold time

J, K, PE, D

n

to CP

ns

Figs 8 and 9

f

max

maximum clock pulse

frequency

MHz

Fig.6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74HCT1G14 | Inverting Schmitt-trigger(反相施密特觸發(fā)器) |

| 74HCT1G66 | Bilateral switch(雙向開關(guān)) |

| 74HCT20 | Dual 4-input NAND gate(雙4輸入與非門) |

| 74HC20 | Dual 4-input NAND gate |

| 74HCT21 | Dual 4-input AND gate(雙4輸入與門) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74HC1958 | 制造商:PHI 功能描述:74HC195D PHIL'88 |

| 74HC195J | 制造商:Motorola Inc 功能描述: |

| 74HC195N | 制造商:NXP Semiconductors 功能描述: |

| 74HC1G00 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2-input NAND gate |

| 74HC1G00GV | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2-input NAND gate |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。